📑

メモリアクセスのレイテンシ測定

本記事は CPU (プログラム) が何らかのメモリアクセスを行ってから、実際にデータが CPU に届くまでのメモリアクセスのレイテンシ測定についてまとめています。

メモリアクセス時の遅延要因

パッと思いつくものでも以下の要因が考えられます。

- L1/L2キャッシュのサイズ

- キャッシュミス (大きなデータをランダムにアクセスすればするほどキャッシュミスは起きる)

- チップ内部のバス (CPU -> DRAM) で消費するサイクル

- DRAM コントローラや DRAM 自体の遅延

連結リスト (Linked List) を使った測定

自分が知る限り、自身でプログラムを作成してメモリアクセスの遅延を図る方法は、連結リストを使う方法です。具体的には、mallocなどで特定サイズのメモリを確保し、その確保した領域で連結リストをランダムに繋げていき、そのランダムに繋がった連結リストを最初から最後までアクセスしていって、そのアクセスにかかる時間を計測するというものです。

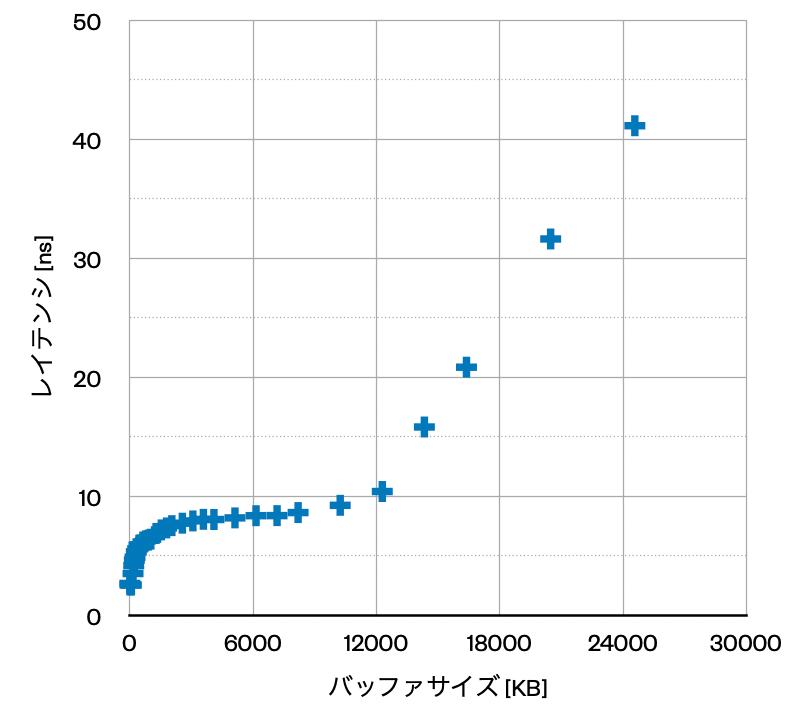

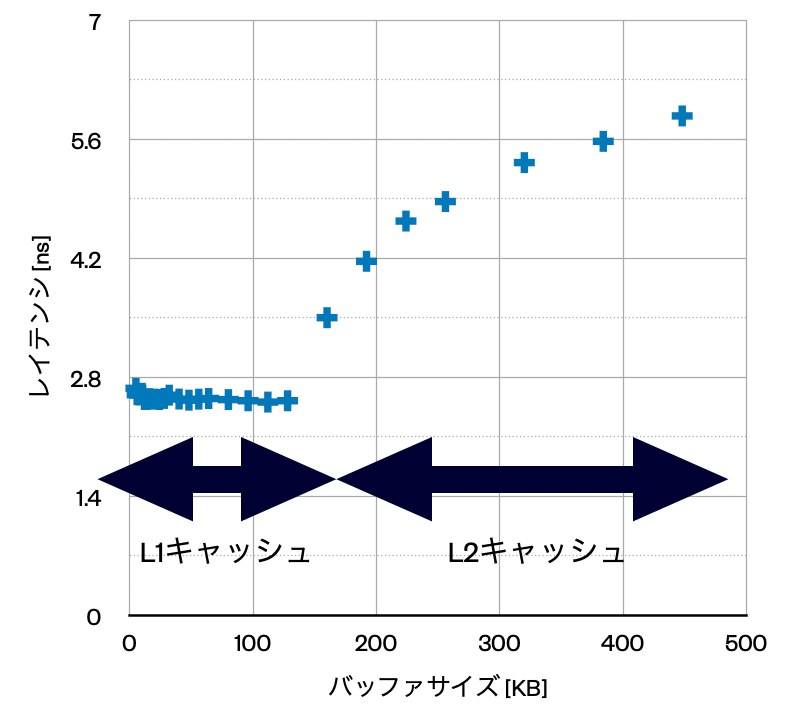

確保するデータのサイズが小さければ、ランダムアクセスしてもキャッシュミスを起こす可能性があまりなく、例えばL1キャッシュ内のアクセスで済むためメモリアクセス時の遅延が小さくなります。一方で、データサイズが大きくなればなるほど、L1及びL2キャッシュでもキャッシュミスを起こすようになり、レイテンシの値が大きくなります。

このように、確保するデータサイズを小さいものから大きいものに少しづつ変えていきながら、そのアクセスにかかる遅延を計測します。一般的には、L1キャッシュのサイズ、L2キャッシュのサイズなどの境界を境にメモリアクセスにかかる時間が増えると思います。

サンプルプログラム

以下のコードを参考にして下さい。READMEの手順でビルドすれば実行可能です。

一般的な?測定方法

LMbench

LMbench は、ネットワーク、メモリ、ファイル・システムなど、システムのさまざまな構成要素のパフォーマンスを測定するためのベンチマーク・ツールです。

mbw

mbwはどちらかというとメモリ帯域のベンチマークソフトです。

インストール方法:

sudo apt install mbw

ベンダー提供のツール

これはベンダー次第ですが...

Discussion