Vitis Platform の作成1(ハードウエアデザインの作成)

はじめに

XilinxのZynqシステムでARMとFPGAを使ったEmbeddedシステムを開発するためにはVitisによるス組み込みカスタムプラットフォームの作成が必要になります。

今回はこのプラットフームの作成手順について確認して行こうと思います。

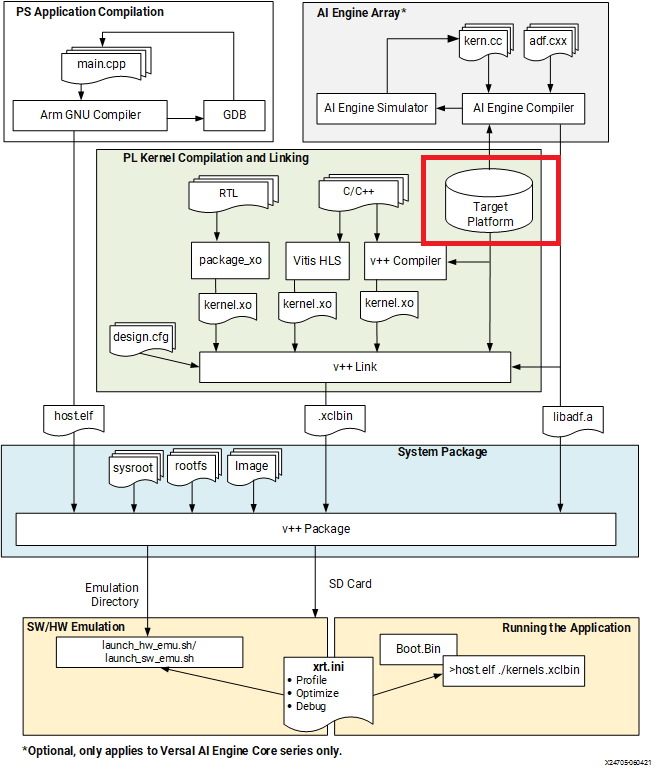

※下図の赤枠部分に相当します。

Vivadoプロジェクト生成

Vivadoでハードウエアデザインを作成して行きます。

ハードウエアデザインはVivadoで生成します。以下のコマンドでVivadoを起動します。

source /tools/Xilinx/Vitis/2020.1/settings64.sh

vivado &

Vivadoが起動したら新規プロジェクトを作成します。

[File] -> [Project] -> [New]を選択します。

Project Nameでzcu104_custom_platformと指定して Nextをクリックします。

|

|---|

Vitisプラットフォームを生成するので、Project is an extensible Vitis Platformにチェックを入れてNextをクリックします。

|

|---|

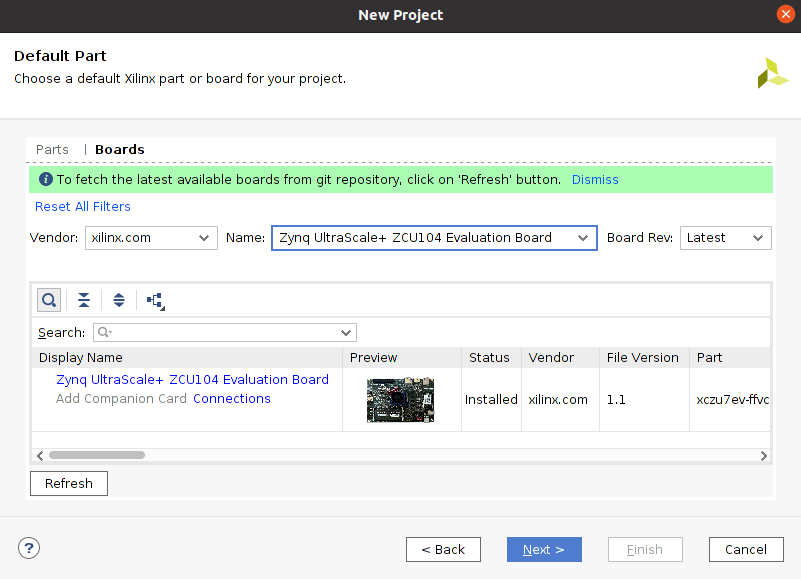

次の画面に進んだら、ZCU104ボードを選択してNextボタンをクリックします。

※boardfileがない場合はRefreshボタンをクリックしましょう。

|

|---|

確認画面が表示されるのでFinishをクリックしてVivadoプロジェクトを生成します。

|

|---|

IP追加(Zynq UltraScale+ MPSoc)

生成されたVivadoプロジェクトから、[Project Manger] -> [IP INTEGRATOR] -> [Create Block Design]をクリックします。

ダイアログが表示されるのでDesign Name = systemに変更してOKをクリックします。

|

|---|

Diagram画面が表示されるので画面を右クリックしてAdd IPを選択します。

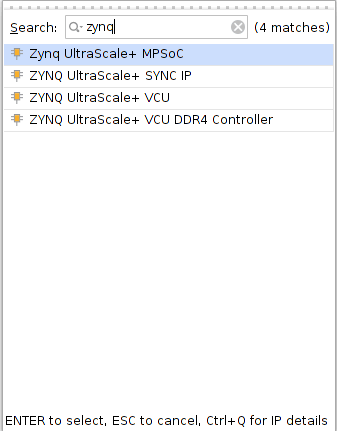

IPリストが表示されるので、その中からZynq UltraScale+ MPSoCを選択してダブルクリックします。

|

|---|

Diagram画面上Zynq UltraScale+ MPSoCが追加されます

ここで画面上部にRun Block Automationが表示されるので、その文字をクリックします。

|

|---|

以下の画面が表示されるのでOKをクリックします。

|

|---|

IP追加(Clocking Wizard)

同様の手順で、今度はClocking Wizardを選択してダブルクリックします。

|

|---|

Diagram画面上にclk_wiz_0が追加されます。

Clocking Wizardの設定をしていきます。Clocking Wizardをダブルクリックして設定画面を開きます。Output Clocksタブを選択しclk_out1=100Mhz, clk_out2=200Mhz, clk_out3=400Mhzに設定します。

|

|---|

また、画面下部にあるReset TypeをActive Lowに設定します。

OKをクリックして設定画面を閉じます。

|

|---|

IP追加(Processor System Reset)

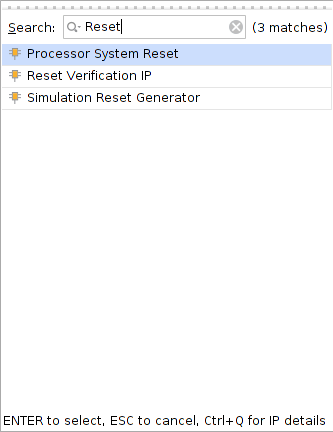

同様の手順で、今度はProcessor System Resetを選択してダブルクリックします。

|

|---|

Diagram画面上にProc_sys_reset_0が追加されるので、選択してCtrl-Vで4つ複製します。

clk_out番号と紐づけたいため、proc_sys_reset_0は削除しておきます。

|

|---|

Diagram画面上部にあるRun Connection Automationをクリックします。

Run Connection Automation画面が開きくので、以下を設定します。

- clk_wiz_0のclk_in1の

ClockSourc = zynq_ultra_ps_e_0/pl_clk0 - proc_sys_resetのインスタンス毎に

ext_reset_inのSelectBoardPartInterface = customSelectManualSource = zynq_ultra_ps_e_0/pl_resetn0

- proc_sys_resetのインスタンス毎に

slowest_sync_clkを- proc_sys_reset_1の

ClockSource=/clk_wiz_0/clk_out1 - proc_sys_reset_2の

ClockSource=/clk_wiz_0/clk_out2 - proc_sys_reset_3の

ClockSource=/clk_wiz_0/clk_out3

- proc_sys_reset_1の

最後に全てのチェックボックスがチェックされていることを確認してOKをクリックします。

|

|---|

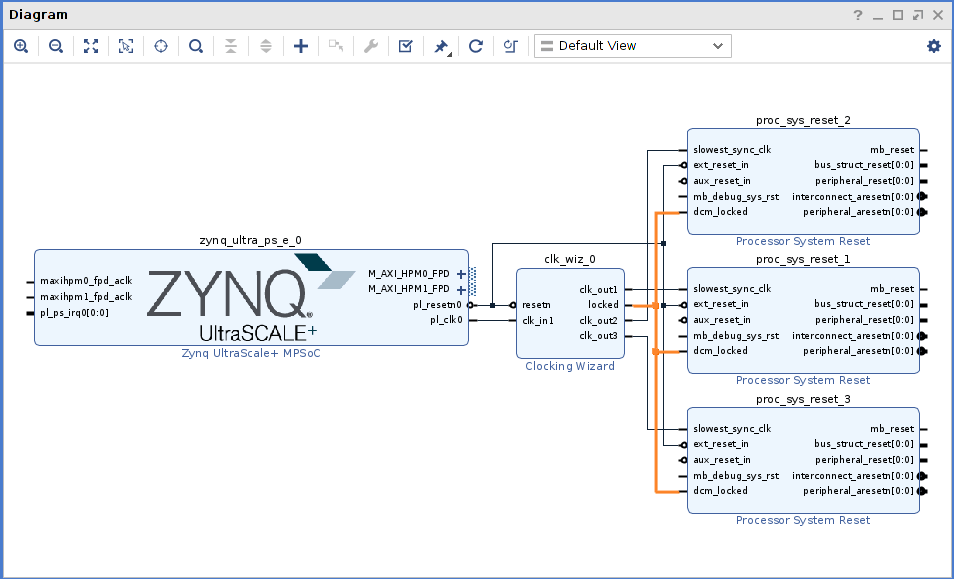

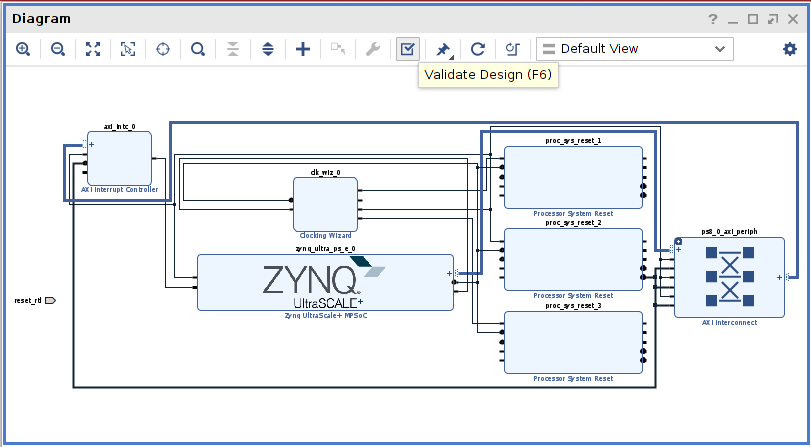

以下のようにDiagram画面上の各モジュールが結線されることが確認できます。

|

|---|

clk_wiz_0のlocked信号とproc_sys_resetのdcm_lockedを接続します。

|

|---|

Clockの設定

Vivadoの[Window] -> [Platform Setup]を選択してPlatform Setup画面を開きます。

[Settings]から[Clock]タブを選択します。

clk_wiz_0のOutput Clocksで生成した各clock(clk_out1、clk_out2、clk_out3)を有効にします。IDを1、2、3に変更し、デフォルトclockをclk_out2に設定します。

|

|---|

割り込みの設定

プラットフォームから割り込みコントローラを制御できるように設定します。

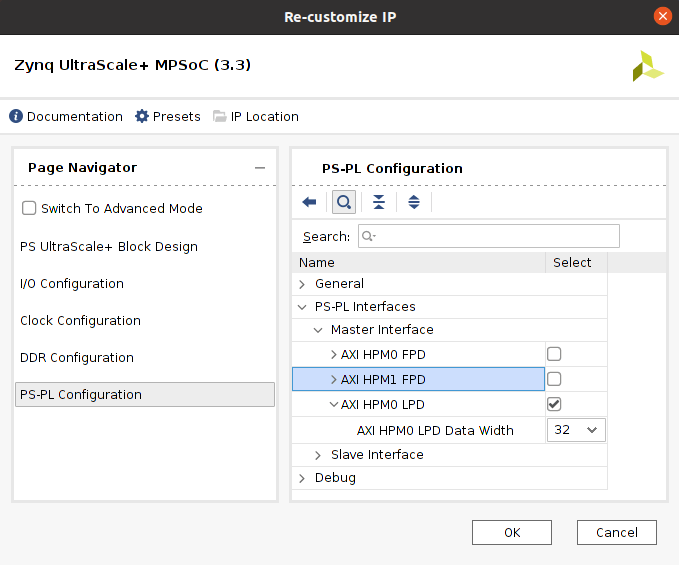

Zynq UltraScale + MPSoCの割り込みコントローラを設定します。

Diagram画面上のZynq UltraScale + MPSoCをダブルクリックして設定画面を開きます。

AXI HPM0LPDオプションを有効にし、データ幅設定を32にします。

AXI HPM0FPDとAXIFPM1FPDは無効に設定してOKをクリックします。

|

|---|

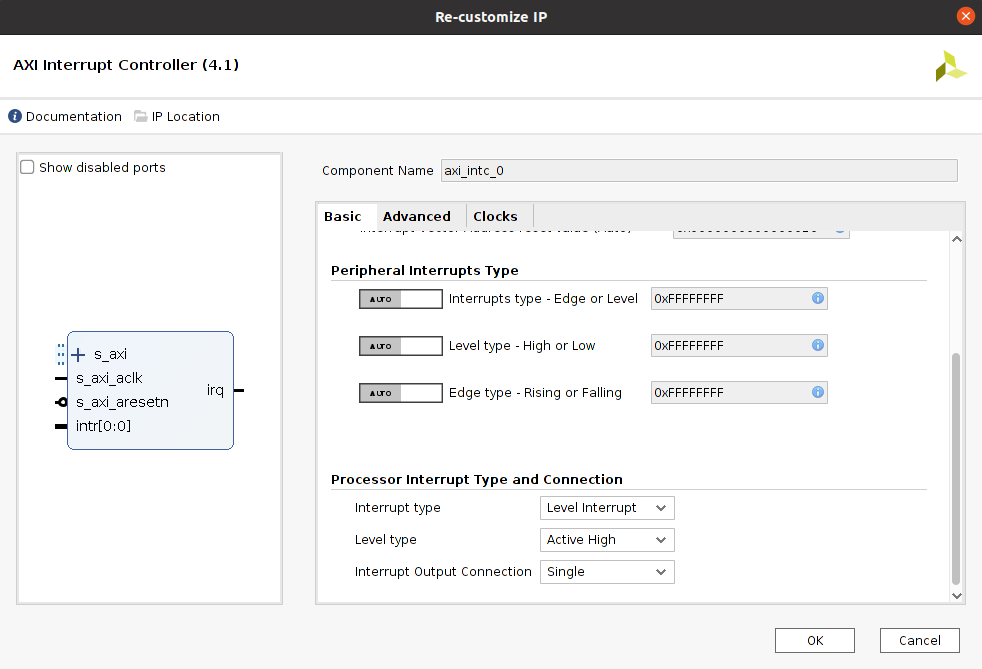

別途FPGA側にも割り込みコントローラIPを実装します。

Diagram画面を右クリックしてAdd IPを選択し、AXI Interrupt Controllerを指定します。Diagram画面上に生成されたAXI Interrupt Controllerブロックをダブルクリックして設定画面を開き、Interrupt Output ConnectionをSingleに設定してOKをクリックします。

|

|---|

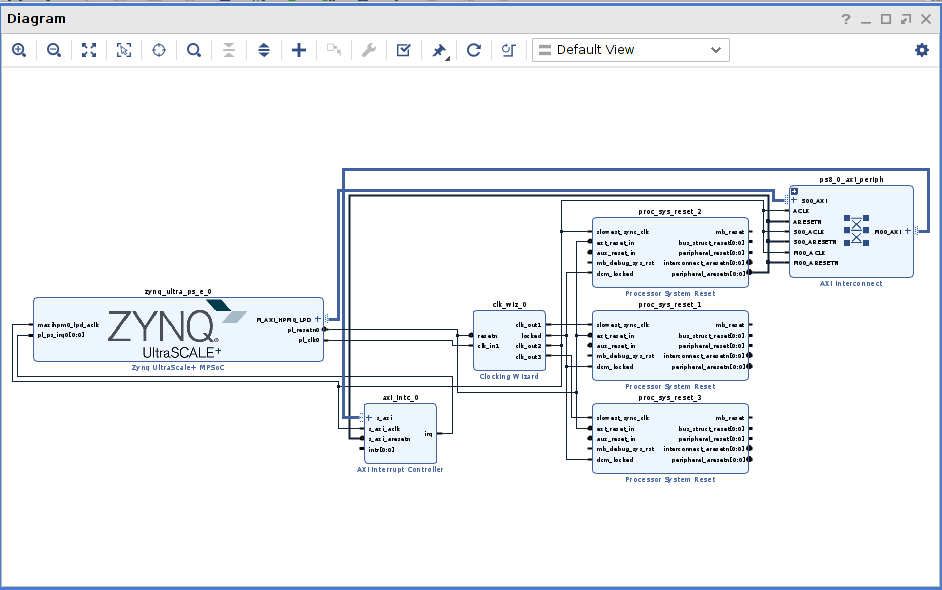

Diagram画面上のRun Connection Automationをクリックします。

axi_intc_0を有効化し、Clock Source for Slave interfaceとClock Source for Master interface に clk_wiz_0/clk_out2(200 MHz)を指定し、OKをクリックします。

|

|---|

割り込みコントローラのirqを接続します。

Diagram画面上から、axi_intc_0.irqとzynq_ultra_ps_e_0.pl_ps_irq[0:0]を接続します。

|

|---|

Platform Setup画面を開き、[Settings]から[Interrup]タブを選択し、axi_intr_0を有効化します。

ここまでの結果は以下の通りとなります。

AXIインターフェイス設定

Zynq UltraScale + MPSoCのAXI Mastert/Slave interfaceを有効にします。

|

|---|

AXI InterconnectのAXI Master interfaceを有効にします。

|

|---|

Zynq UltraScale + MPSoCのAXI Slave interfaceを有効にします。

XSAファイルのエクスポート

DiagramのValidate Designのアイコンをクリックしてデザインの検証を実施します。

|

|---|

以下の警告メッセージが出ますが、プラットフォーム実行カーネルビルド時に解決される問題なので、ここでは無視しても大丈夫です。

|

|---|

デザインTOPのラッパーを生成します。

Sourceタブの[Design Sources] -> [system (system.bd)]を右クリックしてCreate HDL Wrapperを選択します。

|

|---|

Let Vivado manage wrapper and auto-updateを選択してOKをクリックします。

|

|---|

最終的なデザインを生成します。

Flow Navigatorの[IP INTEGRATOR] -> [Generate Block Design]を選択します。

以下の画面が表示されます。Synthesis OptionsをGlobalに設定してGenerateをクリックします。

|

|---|

最後にプラットフォームをエクスポートします。

Vivadoのメニューから[File] -> [Export] -> [Export Platform]を選択して、ウィザードを起動します。

|

|---|

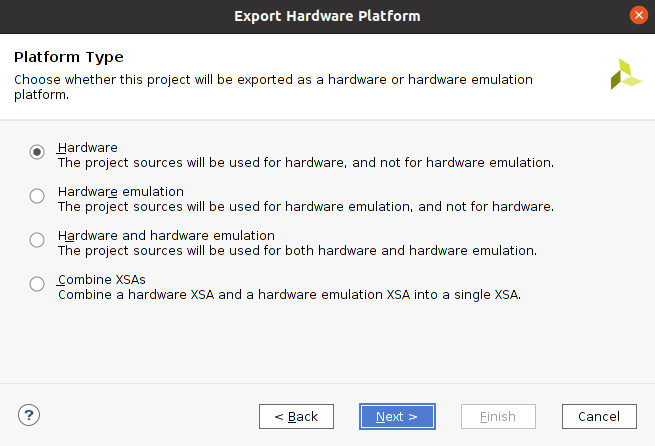

ウィザードの最初のページはNextをクリックして次のページに進みます。

次のページではPlatform TypeにHardwareを選択してNextをクリックします。

|

|---|

Platform StateにPre-sysnthesisを選択してNextをクリックします。

|

|---|

Platform Propertiesを設定して、Nextをクリックします。

|

|---|

XSA file nameにzcu104_custom_platform_hwを設定してFinishをクリックします。

プロジェクトフォルダzcu104_custom_platform直下にzcu104_custom_platform_hw.xsaファイルが生成されていることが確認できました。

以上で、ハードウエアデザインの作業は完了です。

次はソフトウエアプラットフォームの作成を見ていこうと思います。

Discussion