三角波生成回路の作成

はじめに

電子工作初学者の備忘録です。本記事ではLTspiceによるシミュレーションと実際の回路制作を通じて三角波生成回路への理解を深めていきます。

三角波生成回路は積分回路とヒステリシスコンパレータの組み合わせで実現できます。記事の前半で積分回路、ヒステリシスコンパレータの説明を、後半で三角波生成回路の説明と実装を行います。

積分回路

単純な積分回路

図1:積分回路

図1は一番シンプルな積分回路の例です。構造としては反転増幅回路の帰還抵抗をコンデンサに置き換えた回路となっています。入力電圧

シャント抵抗付き積分回路

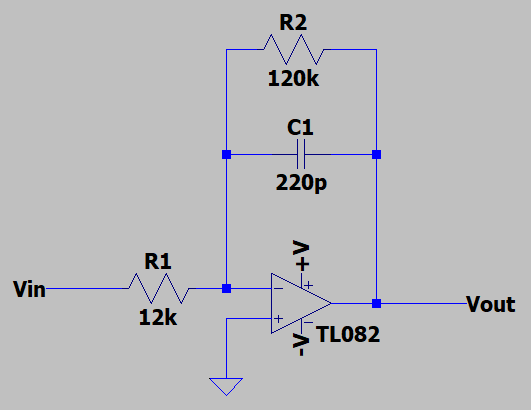

図2:シャント抵抗付き積分回路

図2はコンデンサ

交流成分と直流成分の境界は式(2)のカットオフ周波数が目安になります。

入力信号の周波数を

続いて、シャント抵抗が出力電圧に与える影響について考えます。図2の回路の伝達関数は式(3) のように表されます。

式(3) より、シャント抵抗の影響のある

素子の値の決め方

はじめに、出力電圧のゲイン

続いて、

積分時間は周期の1/2であるため、

よって、

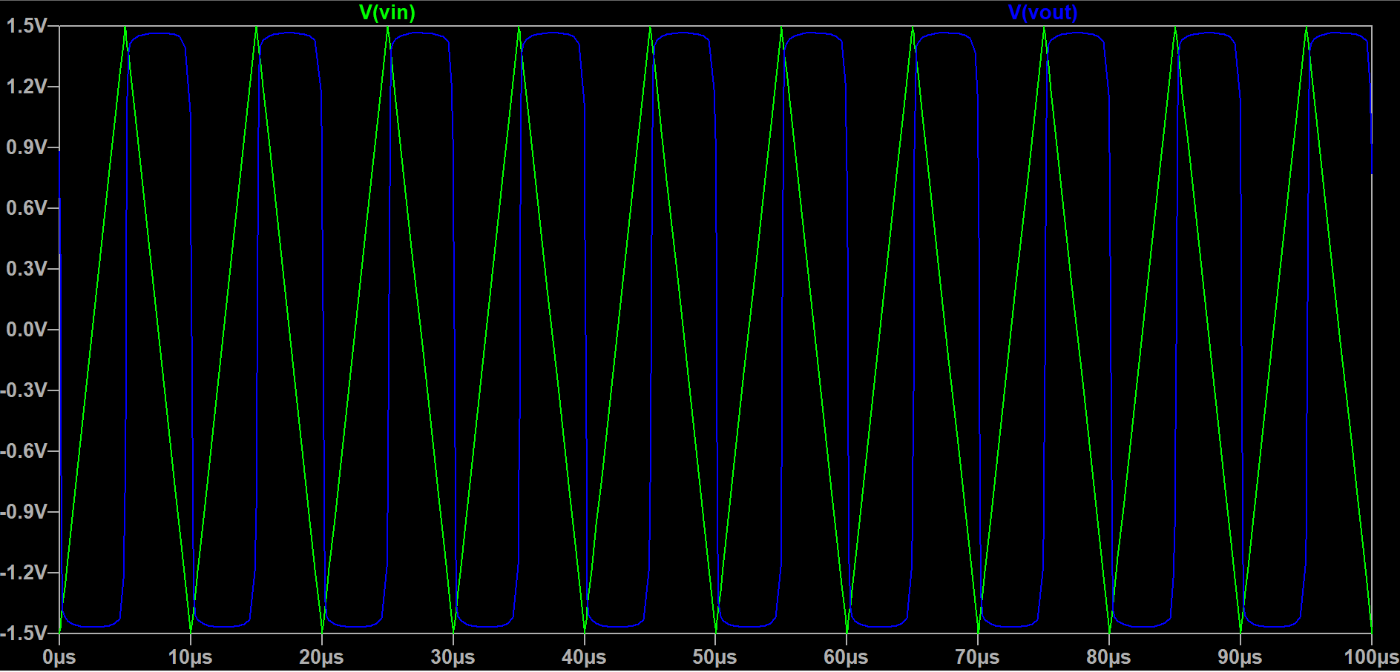

シミュレーション

図3:積分回路シミュレーション結果

図3は以下の条件で積分回路のシミュレーションした結果です。

- オペアンプ

- TL082

- 電源電圧:+3/-3

- 出力飽和電圧:+1.5/-1.5

- 入力信号(方形波):

- 周期:10us、

- 振幅:+1.5V、-1.5V

- 素子

-

R_1 -

R_2 -

C_1

-

ヒステリシスコンパレータ

ヒステリシスコンパレータ

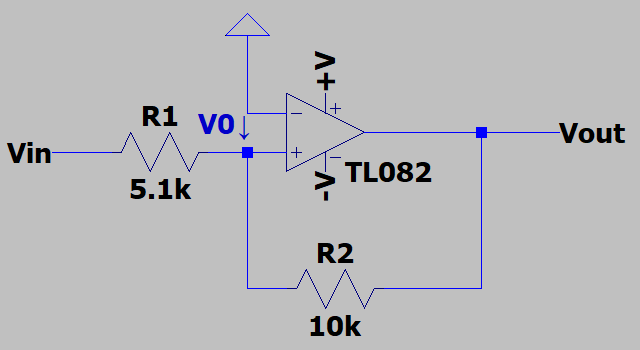

図4:ヒステリシスコンパレータ回路

図4はヒステリシスコンパレータ回路の例です。構造としては反転増幅回路のオペアンプの極性が反転した回路となっています。ヒステリシスコンパレータにおいて、バーチャルショートは成立しません。そのため、オペアンプの負極から正極にかかる電圧を

上式は

シミュレーション

図5:ヒステリシスコンパレータシミュレーション結果1

図5は以下の条件でヒステリシスコンパレータのシミュレーションを行った結果です。

- オペアンプ

- TL082

- 電源電圧:+3/-3

- 出力飽和電圧:+1.5/-1.5

- 入力信号(方形波):

- 周期:1ms、

- 振幅:+1.5V、-1.5V

- 素子

-

R_1 -

R_2

-

上記の抵抗値より、

となります。図5を見てみると、確かに三角波が0.765Vもしくは-0.765Vをまたぐタイミングで

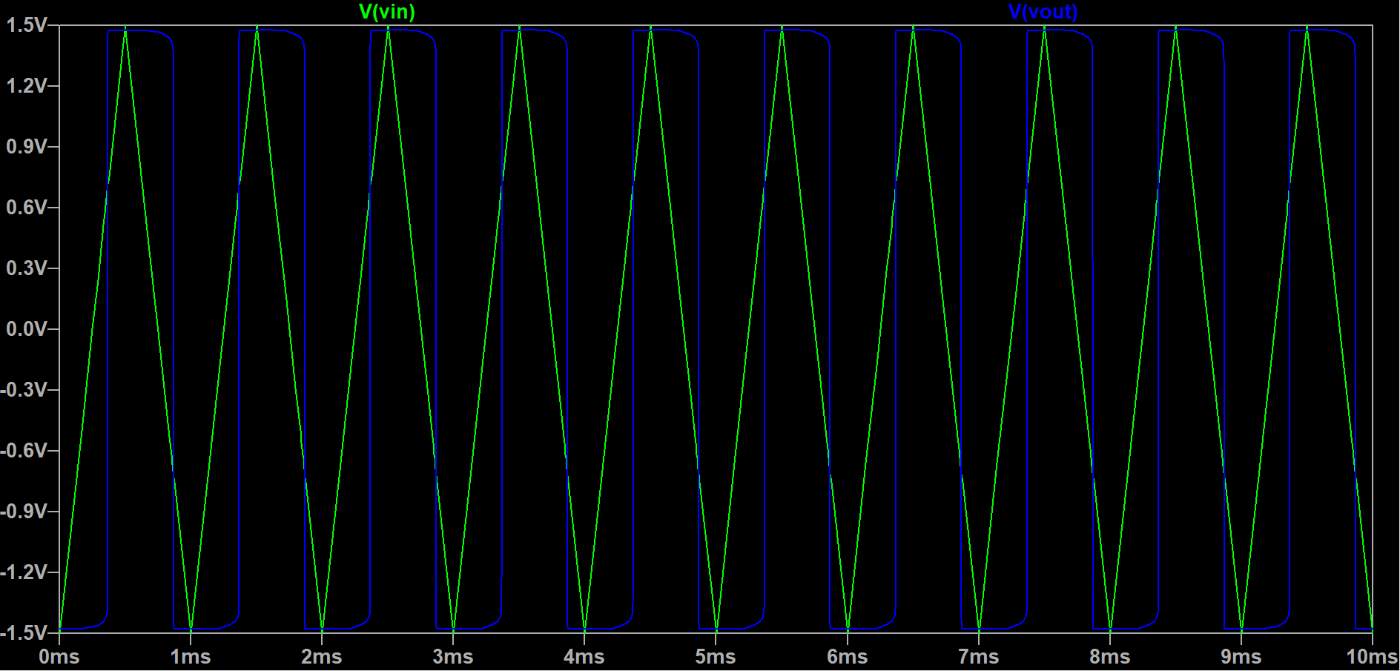

図6:ヒステリシスコンパレータシミュレーション結果2

図6は以下の条件でヒステリシスコンパレータのシミュレーションを行った結果です。

- オペアンプ

- TL082

- 電源電圧:+3/-3

- 出力飽和電圧:+1.5/-1.5

- 入力信号(方形波):

- 周期:10us、

- 振幅:+1.5V、-1.5V

- 素子

-

R_1 -

R_2

-

図6は図5の入力信号の周期を短くした(1ms->10us)場合の結果です。図6は三角波が閾値(+0.765/-0.765V)をまたぐタイミングと

これはオペアンプの過負荷回復時間による出力電圧の遅延が原因であると考えられます(違うかもしれません)。そのため三角波に対して

しかし、三角波生成回路に使用する場合は問題になります。三角波生成回路はヒステリシスコンパレータと積分回路がループした回路です。ヒステリシスコンパレータにおける遅延は積分回路における三角波の生成に影響を及ぼし、その三角波は自分自身の入力となります。結果として生成される三角波の周波数は意図したものより低くなります。高周波数を扱う場合は、オペアンプの代わりにコンパレータを使用するのが無難かもしれません。

三角波生成回路

三角波生成回路

図7三角波生成回路

図7は積分回路とヒステリシスコンパレータを組み合わせて生成した三角波生成回路です。左側がヒステリシスコンパレータ、右側が積分回路で、ヒステリシスコンパレータが出力した方形波が積分回路の入力信号に、積分回路の出力した三角波がヒステリシスコンパレータの入力信号となっています。

三角波の周期

時刻

式(5)と式(7)より、周期

式(8)を用いて図7の回路が生成する三角波の周波数を求めてみます。

各素子の値は

周期44.88us、つまり約22kHzの三角波が生成されることがわかります。

シミュレーション

図8:三角波生成回路シミュレーション結果1

図8は以下の条件で三角波生成回路のシミュレーションを行った結果です。

- オペアンプ

- TL082

- 電源電圧:+3/-3

- 出力飽和電圧:+1.5/-1.5

- 素子

-

R_1 -

R_2 -

R_3 -

C_1

-

三角波の振幅と周波数はおおよそ理論値と一致しています。しかし、振幅は理論値である1.53V(+0.765/-0.765V)よりも若干大きく、周波数も理論値の22kHzよりも若干小さい20kHzとなりました。これはヒステリシスコンパレータのシミュレーションで考察した過負荷回復時間が原因であると考えられます(違うかもしれません)。

実装

図9:三角波生成回路の実験の様子

図9は左から、電源回路、三角波生成回路、オシロスコープです。電源回路ではDC6Vをバッテリ・スプリッタ回路で3Vずつに分圧しています。電源の実測値は

図10:オシロスコープの表示

図10はオシロスコープの表示をズームしたものです。周波数は19.574Hz、波形の最大値は1.09V、最小値は-1.21V、波形全体は-0.06Vオフセットしています。振幅は理論値より大きく、周波数は理論値より小さくなりました。また、三角波はきれいな左右対称の三角形ではなく、上凸の頂点が本来よりも右に寄っています。

振幅と周波数の実測値が理論値とずれている現象は素子の実測値が理論値と異なることやオペアンプの過負荷回復時間が原因であると考えられます(違うかもしれません)。三角波が左右非対称になった原因は調査中です。わかり次第追記しようと思います。

まとめ

LTspiceによるシミュレーションと実際の回路制作を通じて三角波生成回路への理解を深めることができました。実際にやってみないとわからないことってたくさんあるんですね。

Discussion