HW高位合成ツールを使ってnand2tetrisのCPUを動かしてみる 3

の続き

最初のデザイン

Claude3.5 と相談しながら最初にできたのは以下のようなインターフェイスを持つデザイン。CPU命令を格納するROMはテストベンチ側に置き、RAMはcpu内部に置く。また、内部のレジスタ等が観測できるようにしている。

void cpu(

hls::stream<axi_word_t>& rom_in, // ROMから供給される命令の入力

hls::stream<axi_word_t>& rom_addr, // ROMの読み出しアドレス

ap_uint<1>& reset, // Reset 信号

ap_uint<1>& write_out, // RAMへの書き込み信号

word_t& outM, // RAMへの出力データ

addr_t& addressM, // RAMへ書き込む際のアドレス

word_t& pc, // Program Counter

word_t& debug_A, // A レジスタ

word_t& debug_D, // D レジスタ

word_t& debug_instruction // 実行した命令

);

C-simulation

vitis hls のプロジェクトを作る。Target deviceはAcriルームで準備されているXC7A35T-L1CSG324I、周波数は控えめに50MHzとした。Claude3.5が生成したソースとテストベンチを追加し、多少整形した他はほとんどいじらずC-Simulationが動作した。

テストベンチはROMデータとして、nand2tetrisの.hackファイルを直接読み込めるようにした。とりあえず、nand2tetris 5章の最初のプログラムである Add (2+3 を実行して結果をメモリに書き込む) を実行。動作は問題なさそう。

Synthesis

そのままSynthesisに進める。まともに自分で作ったデザイン(といってもAI任せだが)で合成をかけたのは大学の授業ぶりか?ここまで実質HDLを1行も書かずに進んでいることがすごい。(今のところHLSのプラグマ指定もClaude3.5のコードに任せている。)

Fmax 68.79MHz (ただし、Uncertainly 185.19MHz もあるから果たして意味があるのかわからないが。)

Latency 2cycle Interval 3cycle

BRAM 32 FF 162 LUT 650

という結果。この辺の評価は後回しにして動くことを目標として進めてみる。

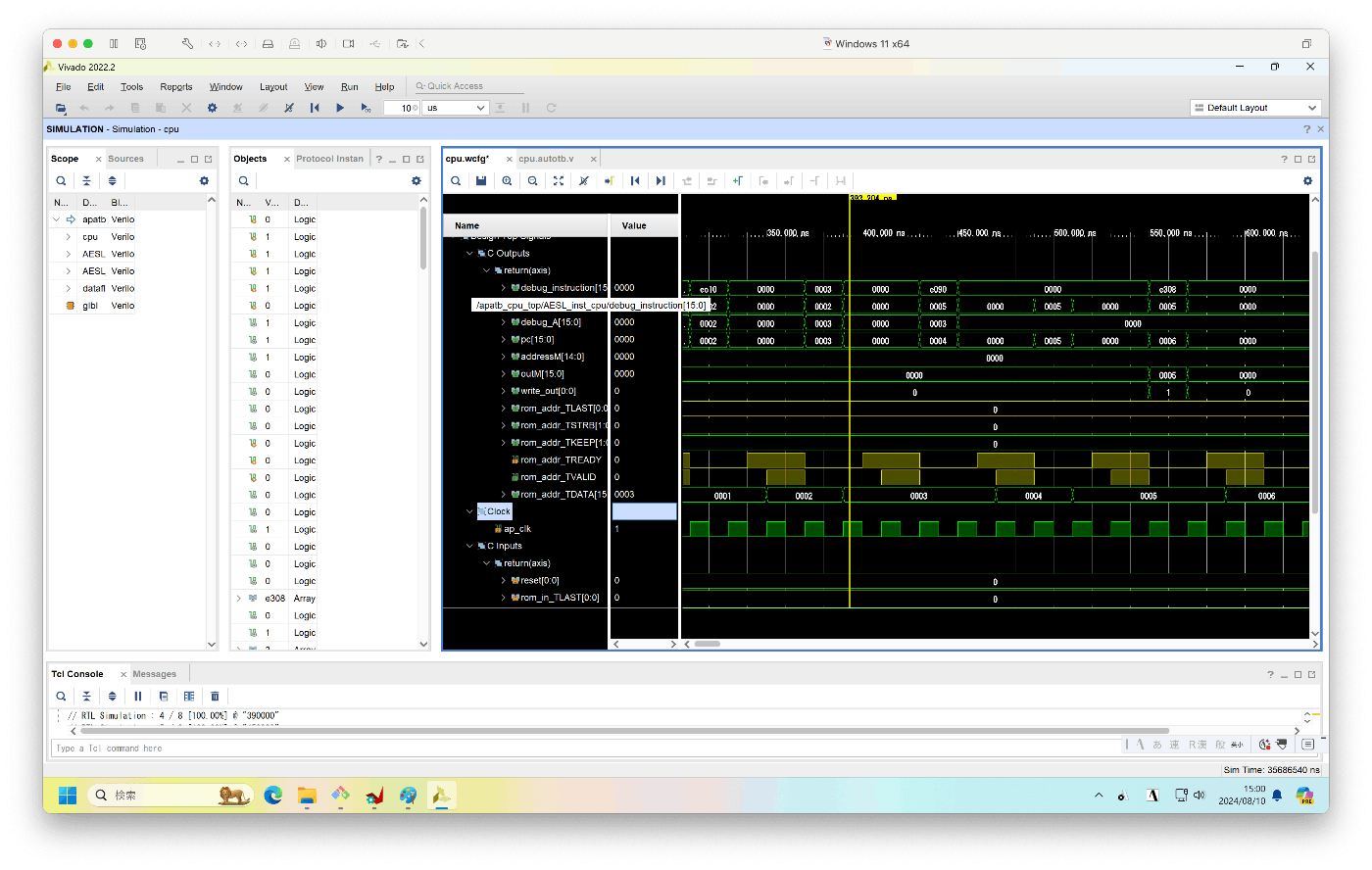

C/RTL Co-simulation

さらにそのままCo-simulationへ。Trace allのオプションを指定し、波形Debugを有効化する。Simulationが終わらないようだったので途中で停止する必要があったが、ちゃんと2+3の計算をしてメモリに5を書き出している様子が確認できた。

しかし、素晴らしい。生成AIにコードを作ってもらいツールに取り込んでたったの 3 step でここまで来てしまった。vitis hlsというツールは本当に使いやすくできているように思う。

もちろん実際の製品レベルには程遠いものだが、はじめの一歩がここまで鮮やかであるとSW技術者[1]でもFPGA設計ができるというのはまんざら嘘でもないと期待してしまう。

次からは実際にAcriルームのFPGA上で動かしてみる。

-

一応、大学の授業レベルではFPGAも触ったことがある。業務でHDLを書いたことはないがHW simulationの結果を使ってDebugはしている。 ↩︎

Discussion