Computer Architecture (LLVM and RISC-V)

GCC

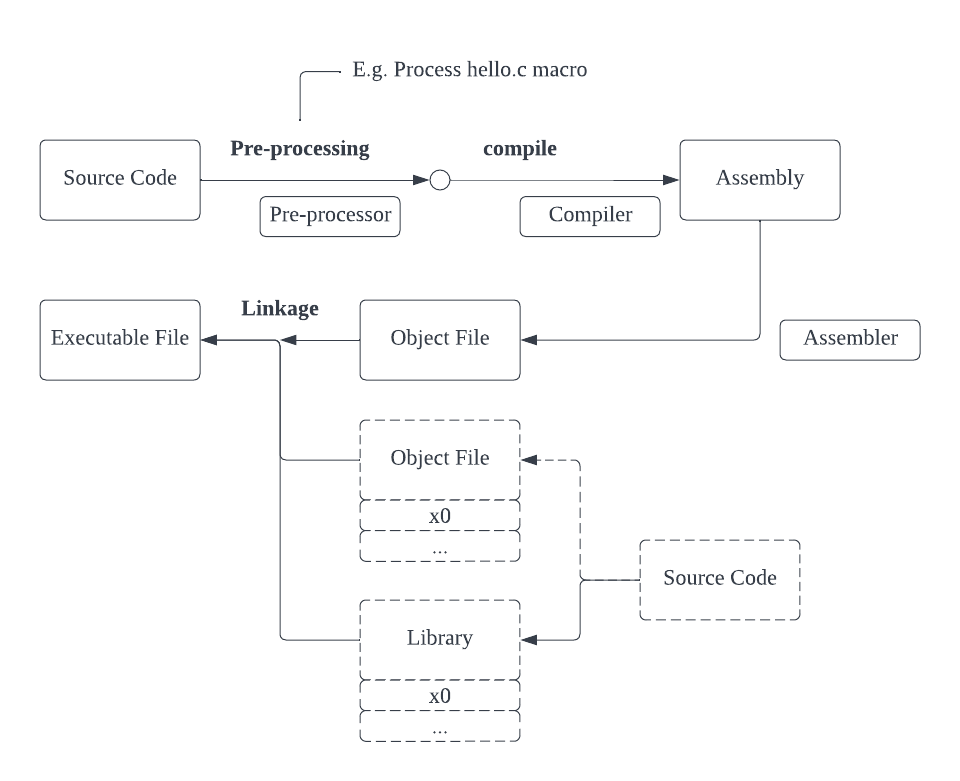

Source-code -> Assmbly-code -> Machine-code (object-file) -> Machine-code (executable-file)

With -S option, gcc stops compiling at assebly stage.

With -o [filename] option you can choose the name of output-file (executable-file).

E.g. gcc -o add add.c -> ls -> add add.c

C.f.

-fno-pic -> Position-Independent Code

-fomit-frame-pointer -> Do not generate frame-pointer

GDB

~/.config/gdb/gdbinit (general)

~/test/teach-yourself-assembler/.gdbinit (project-specific)

CPU Registers Category

- General register (8)

- ESP = Stack-pointer

- Program counter (= EIP-register)

- EFLAGS register

::: info

IA32 has 500< Instructions and over 5000 pages manual

but 90% relies on 25 opcodes - Jim Keller

~= COMET II and CASL II (which only has 28 opcodes and 3 pages manual)

:::

Atmel AVR series comprises ATmega328P and ATTiny13A

ARM = Advanced RISC Machines

- Profiles = A, M, or R

E.g. Armv8.5-A -> Apple A14 Bionic -> Apple iPad Air (10.9'', 4 Gen, Autumn 2020)

Processor-core

-> Probably it means(equals to) Control-unit part inside Processor(CPU)

C.f. Processor > CPU

E.g. ARM Cortex-A/R/M = Groups of ARM Architeture's Processor core, licensed by Arm

E.g. Snapdragon 429 -> (CPU) Arm Cortex-A53 -> Armv8-A

-> Qualcomm gets licence from Arm, then design + manufacture chips like Snapdragon 429

Intel designed and developed IA32 Architecture.

-> AMD designed its 64 bit extension ~= Intel 64

*AMD64 = Intel 64 = x86-64 = x64

Preface

Various Computer Systems

Embedded

PC

Mobile devices

Server

Super computer

Cloud

Edge devices

However all of them comprises Input -> Processor -> Output

- The Processor is composed of General CPU and other specific ones like GPU.

The History of Computer Architecture Evolution

The mechanism of computers remains the same but the following two improvements let it grow in a exponential pace.

Three Key Indicators of Semi-conductor Performance

- Performance (Hz)

- throughput

- latency

- Energy

- Power (W/cm^2)

- Area

-> Dennard Scaling

Besides shrinking semi-conductor,

designing the CPU which can better improve frequency is also important.

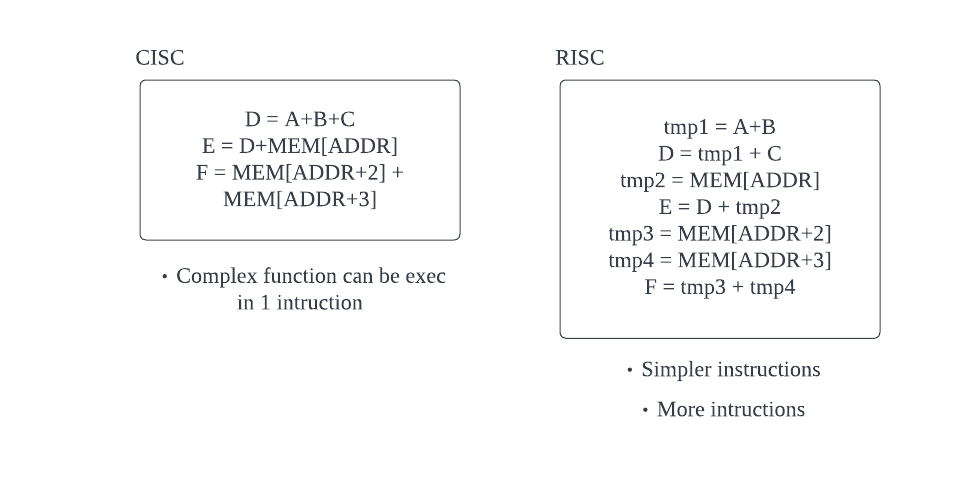

CPU Design Policy: CISC and RISC

- CISC = Complex Instruction Set Computer

- x86 = CISC -> uOP (Micro-operation)

- CISC gets dismantled to simpler uOP then executed

RISC = Reduced Instruction Set Computer

- CISC gets dismantled to simpler uOP then executed

- x86 = CISC -> uOP (Micro-operation)

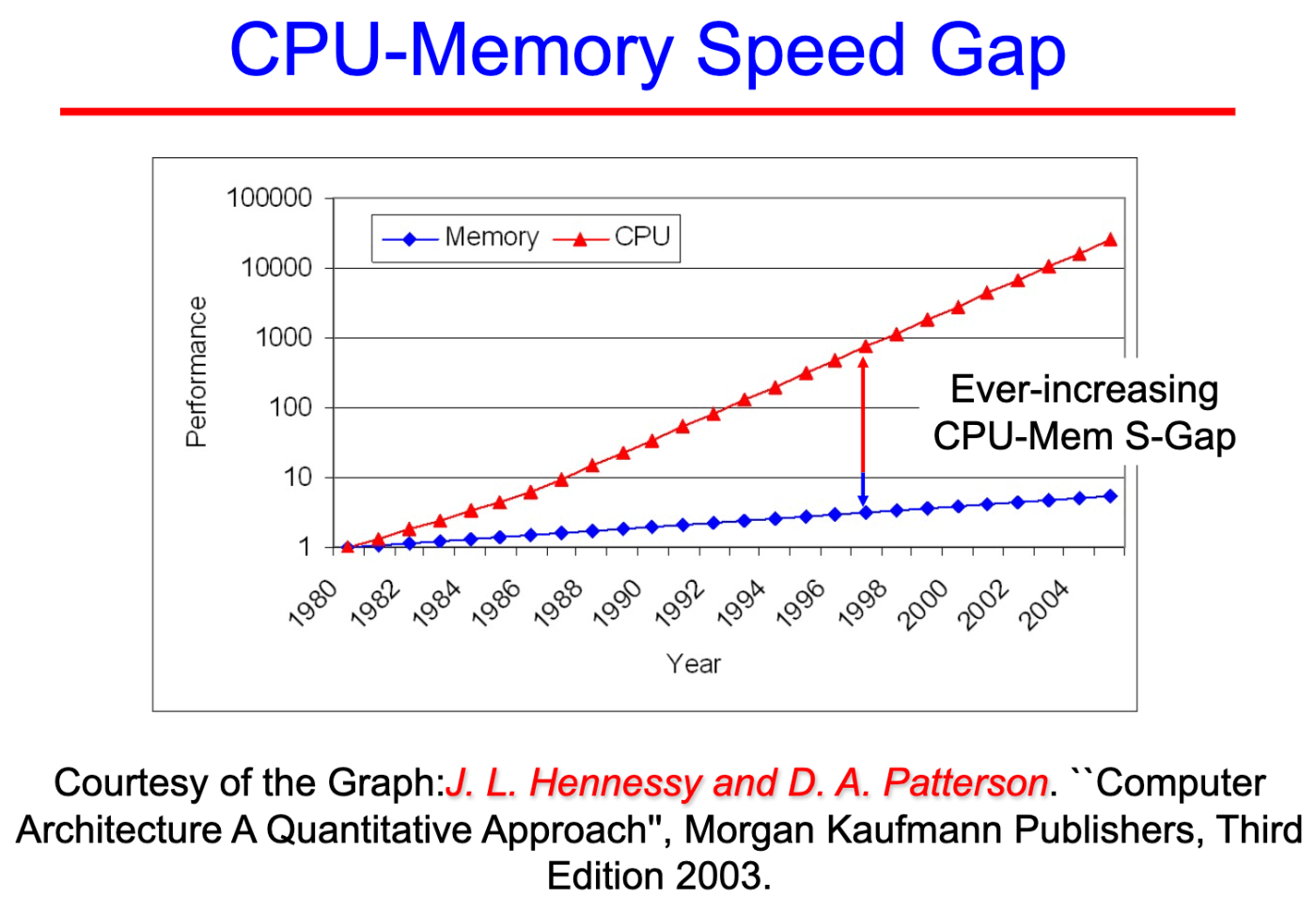

The Wall of Perfomance Improvement: Memory

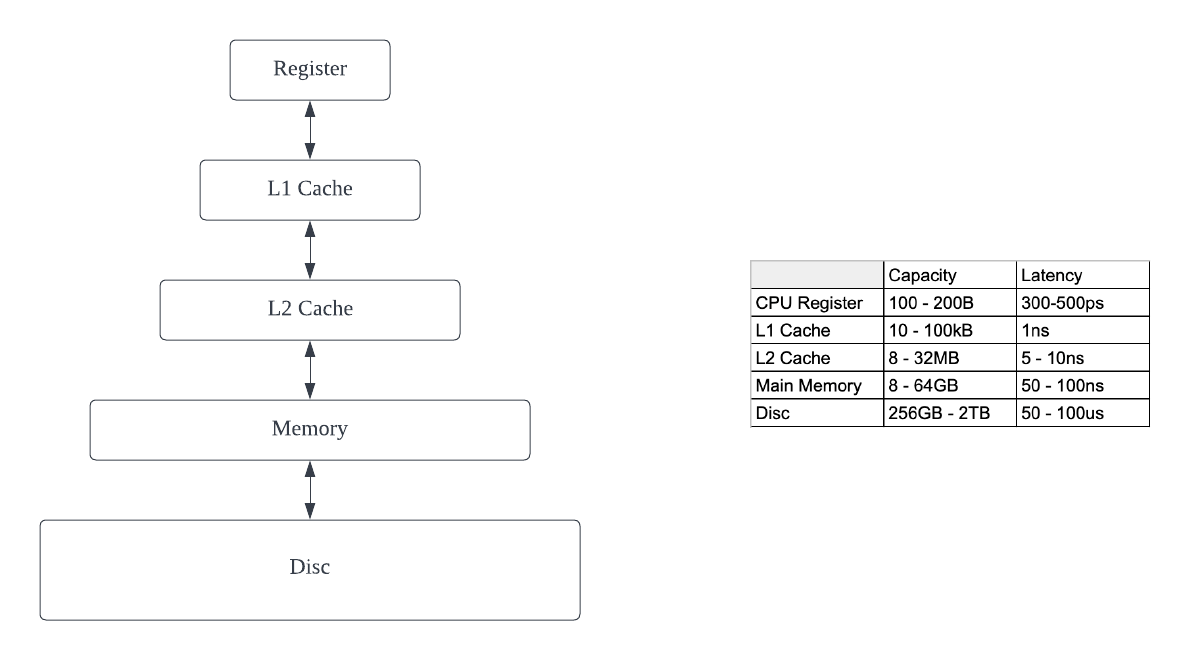

Memory Hierarchy

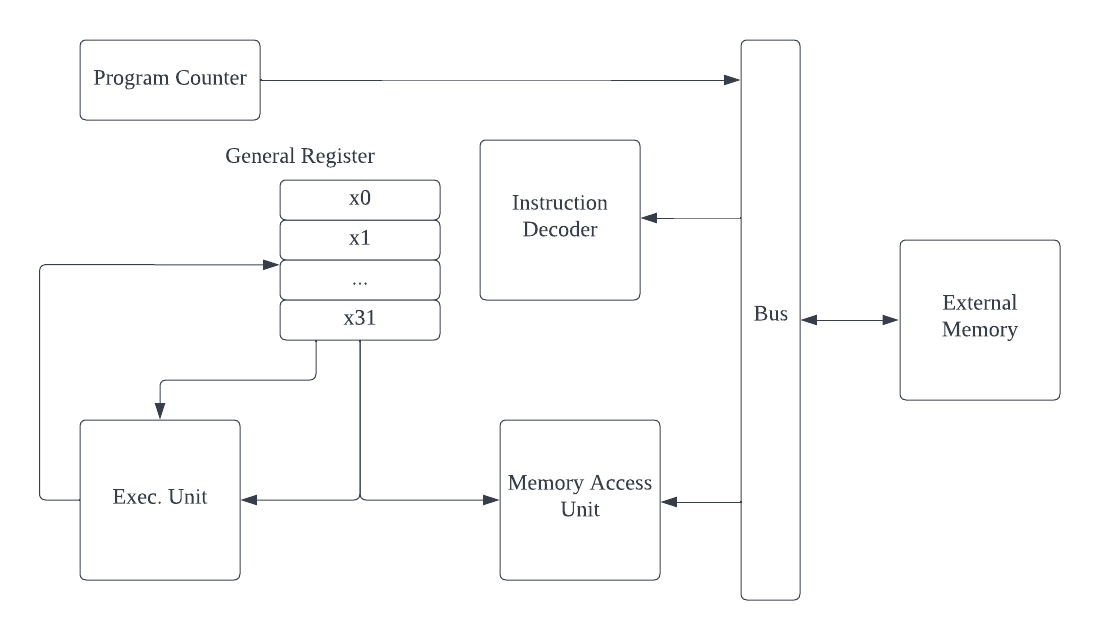

Von Neumann Architecture

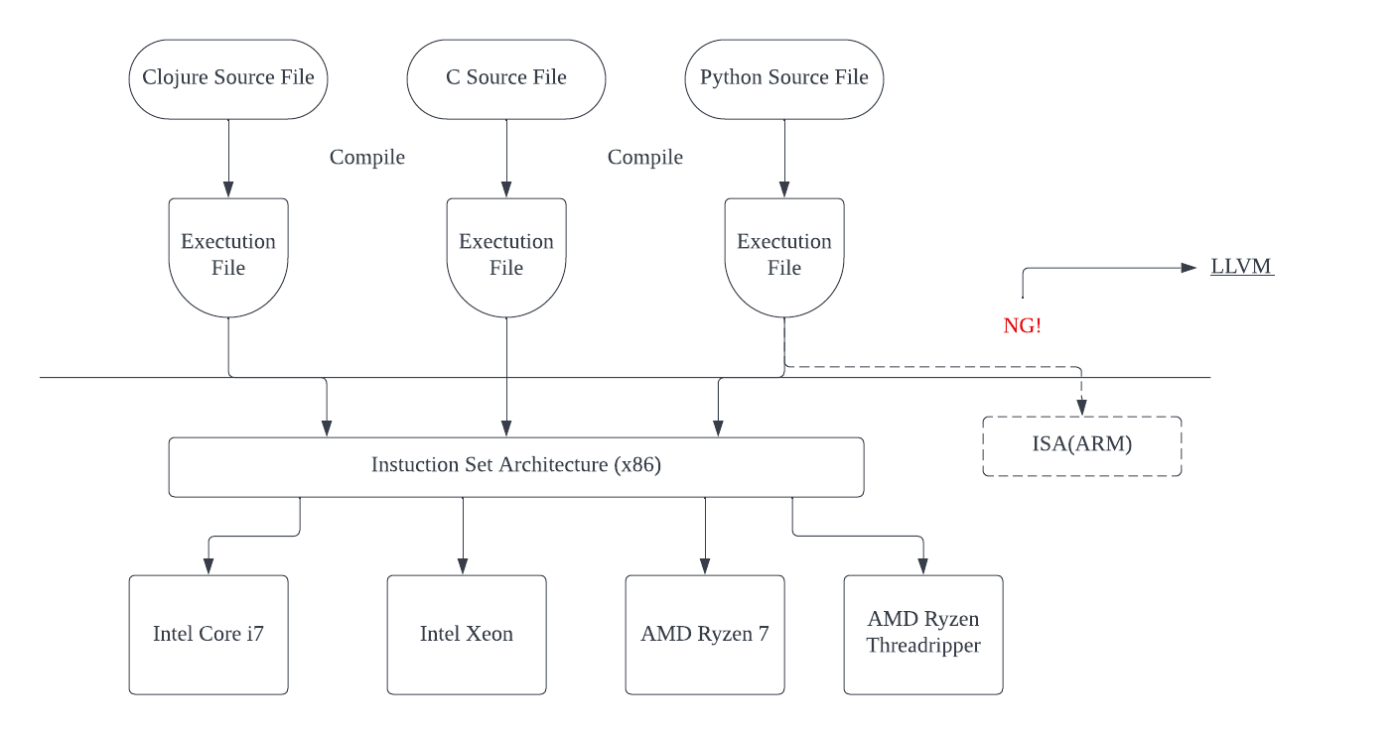

Representative ISAs

-

x86

- In most PC/Servers

- 32B = IA32 and 64B x86-64

-

ARM

- In most smartphones and also edge devices

-

MIPS

- Classic RISC

-

RISC-V

- Simple, Free, and Open ISA

-

Power

- Developed by IBM, it has significant share in super-computers.

-

SPARC

- Developed by Sun MicroSystems, it's influenced by RISC.

C.f.

AArch64/ARM64 is the 64-bit extension of the ARM architecture family.

It was first introduced with the Armv8-A architecture. Arm releases a new extension every year.

ISA

It is the interface of CPU and Program

IS vs ISA

IS is like the language CPU speaks.

ISA is IS with intruction packaged.

Compiler Driver

Assembly and Machine Language in Example

Address RISC-V Machine Language

--------- ---------------------------------

0000000 8537 0001 0113 fd01 0513 c785 3423 0211

0000010 3c23 0091 3823 0121 3423 0131 3023 0281

0000020 20ef 45c0 b783 7581 94b7 0001 b503 0107

...

Machine Language Assebly Language

00018537 : lui a0, 0x18

00018537 : addi sp, sp, -48

00018537 : addi a0, a0, -904 # 17c78 <__trunctfdf2+0x2da>

00018537 : sd ra, 40(sp)

00018537 : jal ra, 1252c <printf>

...

Machine Language is intructions lined in order, followed by their argument (operand).

Skipped the following sections for now.

- Endian

- Speed up techniques for CPU eg Pileline etc

- Not quite understand what/how CPU improved dramatically and what's the current wall for more.

- Details of RISC-V instructions

RISC-V Hands-on

Install riscv-tools

- riscv-sifive-tools

- risc-tools

(sh) > riscv64-unknown-elf-gcc --version

(sh) > spike

# Check installation by these two commands

(sh) > export PATH=/path/to/package:$PATH

# Warning:

# This added path would disappear if restart Terminal