OpenLane:オープンソース RTL2GDSIIフローをガチで見る

OpenLane:オープンソース・スタンダードセルベース ASIC デザインフロー

AWSにPDFがあり(efabless.comが著者)、OpenSource EDAを組み合わせて作ったStandard Cell Digital ASIC向けデザイン・フロー OpenLane. これまでいろいろなツールは個別には利用したことはあるのだが、ピンポイントツールであることやデザイン・オートメーション(EDA)というよりは、CADなイメージのツールが多かったと思う. STAツールやRoutingエンジンがオープンソースで出てきたことがデザイン・フローとして組み合わせて利用しやすくなったのだろうか.

OpenLaneのコアな部分(フロアプラン、P&R、CTS、STA)は、OpenROADのツールやコマンド、STAはOpenSTAを利用している. データベース部分は、OpenDBを使うとのことらしい.

使い方は、README.mdを読めばわかると思うので、

ここでは、デザインフローとしてどうなのかを見ていたいと思う.

OpenLane flow

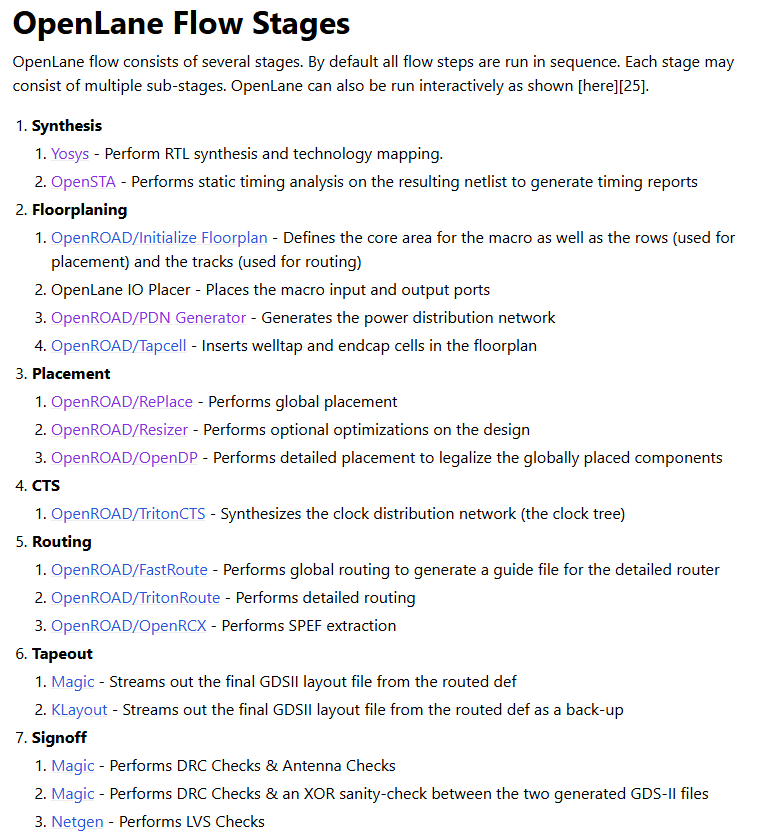

OpenLaneのフローは、次のような構成となっている. コンセプトとしては、人でを介さずにSignoffまで処理することができるというものではある.

もし仮に、そのコンセプトが本当に可能であれば商用EDA製品で実現しているのではないか、と思うのだが・・・最後に愚痴ることにする.

各ステップ毎に確認してみる

- Synthesis

- Yosys: いわゆる論理合成ツール

- OpenSTA:スタティック・タイミングチェック・ツール

- Floorplaning

- IO・ピン配置

- 電源・グラウンド配線

- タップセル:基盤をGNDに、電源をWellに接続するセル配置

- Placement

- グローバル配置(概略)

- 配線負荷の調整:セルサイジング、リピーターセル挿入

- 詳細配置:配置グリッドに乗せる配置処理、ピンアクセス確保配置

- CTS

- クロックツリー形成(クロック・ツリー・シンセシス(合成))

- タイミング最適化(クロックツリー上のセル・ドライバビリティ調整、リピーター挿入)

- Routing

- グローバル配線(概略配線)

- 詳細配線

- RC抽出(抵抗・規制容量抽出)

- Tapeout

- ストリーム形式(GDSII)ファイル出力

- Signoff

- デザイン・ルール(描画規則)チェック:DRC

- 論理・レイアウト検証(LVS)

- レイアウトパターン基本チェック(GDSIIファイル)

この図で、Tapeout・SignOffとなっているところは気に入らない.

本来は、SignOffが終わってから、TapeOut(GDSIIファイルをテープで製造マスク側へ渡すこと)で、その後描画処理して製造プロセス向けに各レイヤのレチクルやマスクが製造されて製造プロセス工程に送られる.

レイアウトパターン基本チェック:sanity checkであり描画データ生成(PG)を保証するチェックではない.

OpenLaneのデザイン・フロー内容は20年~25年くらい前(2000年~2005年)頃にEDAベンダーが提供していたASIC向けデザイン・オートメーション・ツールの構成・テクノロジにいろいろと足りない感じ.

プロセステクノロジ・ノードとしては、~100nm程度(頑張れば)には対応できる かもしれない レベルと思う.

とはいっても、

オープンソース・ツールを組み合わせてここまでできるのはすばらしく、とても関心する.

OpenLaneのOpenROAD部分について

OpenLaneのフローはOpenROADのコマンドを利用しているがOpenROADのフローをそのまま利用しているわけではなく、フローはOpenLaneで作成している.

OpenLaneのフローとOpenROADのフローでは若干異なる部分(フィジカル・オプティマイズの部分のフローの実装が違う)が見られる.

なぜ異なるかというと、コンセプトやポリシーによるものと考えてよい部分.

OpenROADにはOpenROAD flowがありこちらも興味深い

90年代初め、P&R(配置・配線)のステージではタイミング合成は行っていなかった. 配置・配線後の処理でタイミングチェックを実施してECO(エンジニアリング・チェンジ・オーダー)でタイミング収束させていた.

その後に配置・配線にSTA組み込み各ステージでタイミング合成することで大きな手戻りを少なくしてきた経緯はある.

これらが無料でできることはホントに素晴らしと思う.

no-human in the loop RTL to GDS compiler というコンセプト

これはうたい文句みたいなもので、これをそのまま信じるデザイナー(LSI/ASIC/SoC設計者)はいない.

テスト(サンプル)デザインのSPMは、デザイン・サンプルにはなりえない1パスのシリアル・パラレル・掛け算器で構成してあってしかも動作周期はとても遅い. フローが流れるという確認としては良いだろう.

OpenLaneを使ってデバイスを作った事例がいくつも上がっているが、OpenLaneだけで作ったとは一言も書いていない点は言わゆるマーケティング手法によるものなので、OpenLaneだけで製造できると思うのは気を付けたほうが良い.

現実的な設計においては、設計要件は厳しく設計者が相当の手間をかけて実装していて、さらにテクノロジノードとして100nm以下となると製造的な影響や、チップの規模からはチップ上のばらつき問題などのクリア、製造安定性対応などがさらに必要なためゼロタッチでテープアウトは不可能と言わざるを得ない.

具体的には、

OpenSTAは2000年代初期のタイミングツールのレベルなため、OCVやSIには対応しておらずこれらの問題を無視してデバイス製造は無理.

製造安定性についてもCMPなどの平坦化の問題などを含めたDFM関係については、現状はスルーしているように見える. 不良率や歩留まり問題は製品価格への影響が大きく対応は必要となる.

EDAツールの商用版は、これらについては2007年頃TSMCリファレンスフロー7.0(65nmノード)ではクリアしており、OpenLaneは25年くらい前のテクノロジ相当と考えてよさそう.

さらに少し進むと、EM/IR、FinFETルールサポート、Fin-base placement、Low-Vdd、pin access、

3D構造トランジスタ(Fin)、DPA(Differential Power Analysis)とかInFO(Intergate FanOut)、MiM(メタル・インシュレーター・メタル)とか扱うことはたくさん、たくさんある.

だから、これ(OpenLane)だけではとてもじゃないけどテープアウトなんてできない.

近年は、

トランジスタがGAAで、Silicon Photonicsも・・・・

実際問題としては、デザイナー(設計者)への負担は上がるとおもうがEDAツールコストが非常に高いため部分的にオープンソースツールを導入してコスト低減しつつできない部分で商用ツールを利用することも可能とも考えることはできる.

90nmくらいならそうとう頑張ればできるとおもうけど、65nm/40nmはほぼ無理、それ以下は無理かなぁ.

1umくらいのテクノロジノードでミニマルファブを使った小さなデジタルデバイスならコンセプト通りでもできるのかもしれんね.

Discussion