🏩

VivadoによるIP設計 文字表示回路の設計とIP自作

VivadoによるIP設計 文字表示回路の設計とIP自作

はじめに

前回に続き、「FPGAプログラミング大全 第2版」をやる

本投稿では本書7-2~「文字表示回路の事前検証と実機確認」を実施したメモを書きます

前回の続きとして、文字表示回路を設計し、IPパッケージングしてFPGAで動かす

環境

FPGA : Xilinx Zybo Z7-20

OS : WSL2 Ubuntu20.04

開発環境 : Vivado ML edition 2022.1 Linux版

やりたいこと

HDMIでディスプレイに文字を表示する回路を作成する。

文字表示回路の仕様

- 1文字はタテ×ヨコ8ドットずつで構成

- ヨコ80文字、タテ80行表示可能

- 文字コード・文字色の記憶にはVRAMを使用

- 文字パターンを記憶する読み出し専用メモリとしてCGROMを使用

実装

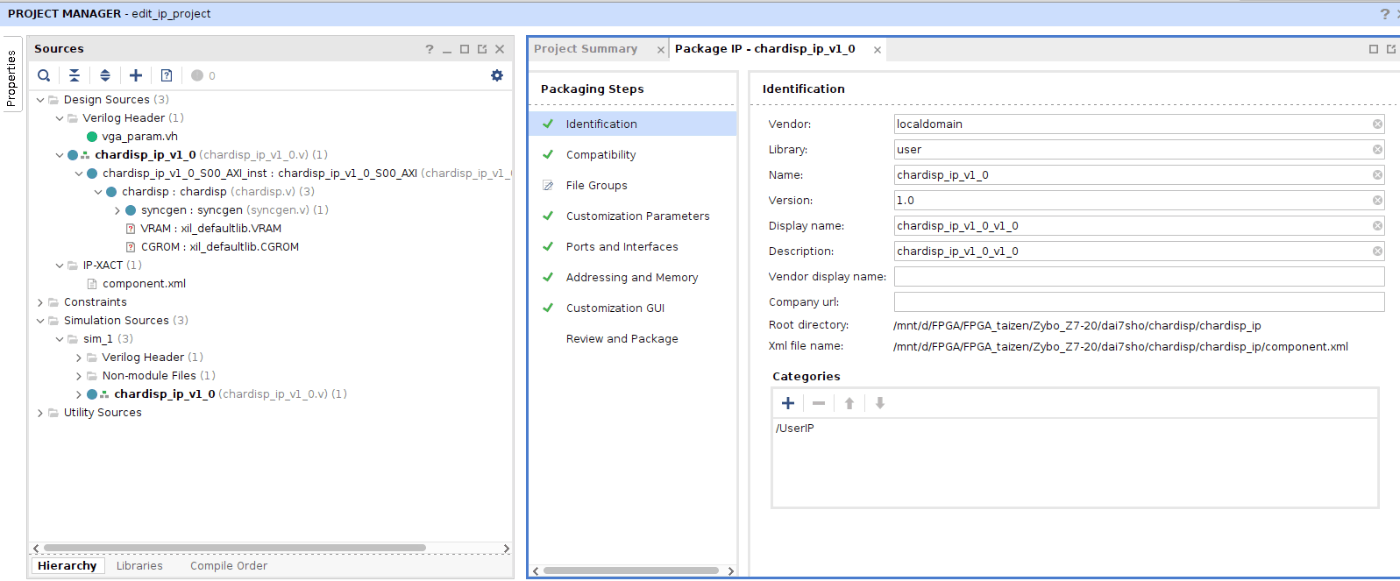

Projectの作成

- Projectの作成 ->Create and package new IP

- Package a specified directory

- 付録のchardisp_ipディレクトリを選択 ->Finish

VRAMとCGROMが不足している

VRAM生成

- Block memory generator IPを追加

- Customize IP

- Memory Type : True Dual Port RAM

表示タイミング読み出し、AXIbus経由でのCPU読み書きを行うため、2系統が必要 - Byte Write Enable : ON

- Byte Size : 8bit

VRANデータ幅は24bitだが、これにより8bitずつ書き込み可能となる - portA/B: Write/Read Width ->24bit , write/read depth : 4096

- Enable Port type : Always enabled

- Memory Type : True Dual Port RAM

Summaryを確認してOK

- Out of context per IP -> GenerateでVRAMが生成される

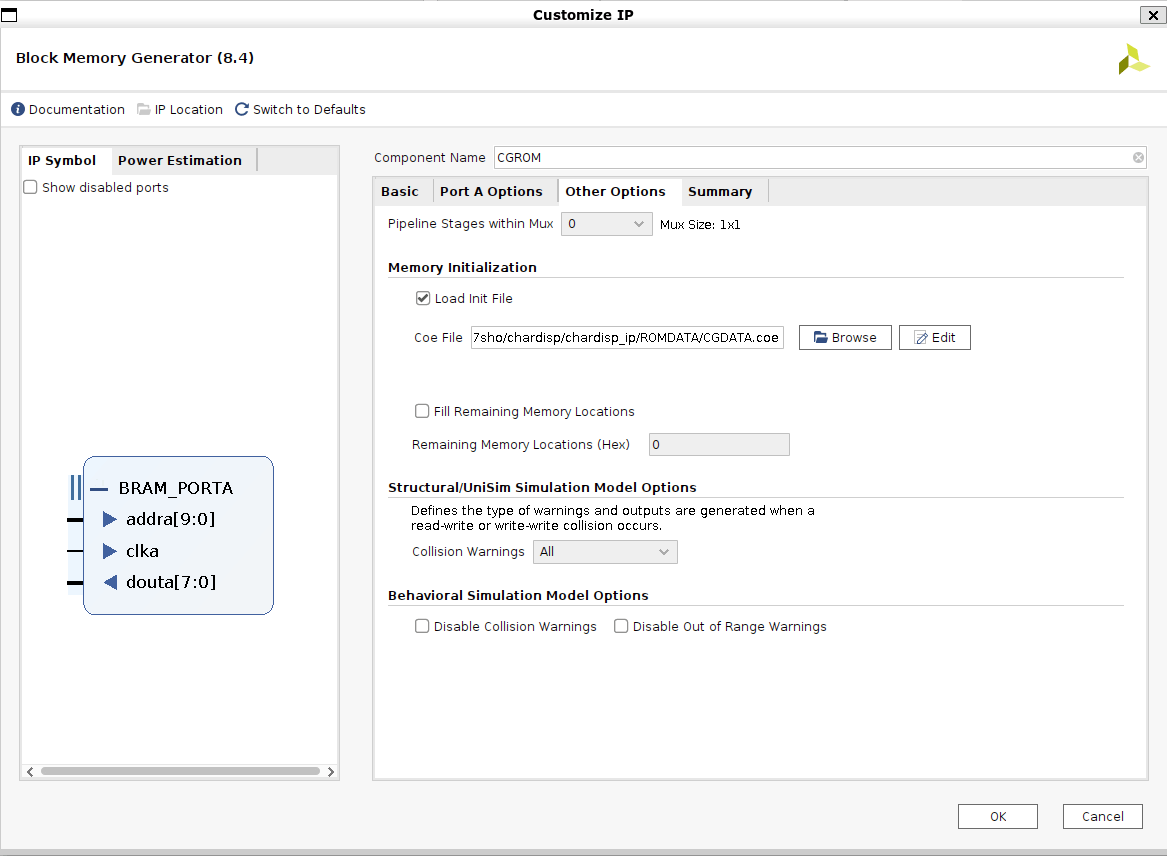

CGROM生成

- Block memory generate IPを追加

- Customize IP

- Memory Type : Single Port ROM

- Port A Width : 8bit

- Port A Depth : 1024bit

- Enable port type : always enabled

- Other option / Memory Initialization -> Load init FIle on

- Coe fileを選択(CGDATA.coe)

Summaryを確認してOK -> Generate

- Re-package IP

文字表示回路のIPが完成

IP catalogからchardisp_ipが呼び出せるようになった

文字表示回路のシミュレーション

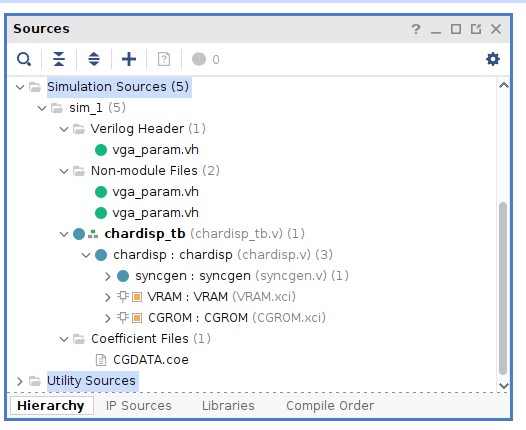

- Simulation用の新規プロジェクトを作成する

- Memoryに値を書き込んでファイルを出力するテストベンチを作成する

手順は以前のパターン表示回路設計時と同じ

こんな感じのヒエラルキーになればOK

Run Simulation

5.1usでResetが解除され、Write EnableがHigh -> CGROMからデータ取得している?

0.85ms辺りでメモリへのWriteDataが終わっている

VGA_DE ->H後、2.7ms辺りからRGB論理が変化し、画像として表示されているのが分かる

InfanViewで書き込まれたデータを確認

シミュレーション完了!!!!!

次回は実機検証を行う

Discussion