【AI駆動開発】AIを活用したVitis HLS設計フレームワークの提案

はじめに

FPGAの回路設計に携わる皆さん、日々の開発でこんな経験はありませんか?

- 「アルゴリズムの仕様変更に、HDLの修正が追いつかない…」

- 「HDLのコーディングに時間を取られている」

- 「タイミングクロージャのための試行錯誤が果てしない…」

これらは、HDL設計者であれば一度は直面する課題です。

そして、その解決策として HLS(高位合成) の存在を知りつつも、次のような疑問から一歩を踏み出せずにいる方も多いのではないでしょうか。

- 「C++で書いた抽象的なコードが、本当に効率的な回路になるのか?」

- 「ビットレベルの制御を手放すなんてあり得ない」

- 「HLS特有の書き方を覚えるくらいなら、自分でHDLを書いた方が早いのでは?」

本記事は、そうしたHLSへの期待と不安が入り混じる全てのハードウェア設計者に向けた、AMD/Xilinx Vitis HLSと生成AIを組み合わせたAI駆動HLS設計の提案です。

筆者について

- 所属: 大学院 情報工学専攻 修士2年

- 専門: FPGA向けHDL設計(Verilog, VHDL)

- EDAツール: Vivado, Vitis HLS

-

HLSへの不信感: 「制御を失うことへの恐怖」

- HDLなら信号やクロックの流れを明確に制御可能

- HLSは物理実装がブラックボックス化し、意図しない回路生成が怖かった

この課題意識を、AIという新しいアプローチで解決できないかという思いが、今回の取り組みの動機です。

なぜAIは直接HDLを書くのが苦手なのか?

AIに「この機能のVerilogを書いて」と頼めば、それらしいコードは出てきます。しかし、実用レベルで信頼できるものは少ないのが現状です。

理由は単純で、AIはハードウェアの物理的制約を理解していないからです。

主な課題

-

タイミング(Timing) ⌛

- FPGA上の配置配線や物理遅延を理解できないため、タイミング制約を満たせないコードが頻発。

-

並行性(Concurrency) ⚡

- HDLの並行動作モデルを正確に把握できず、競合や意図しないラッチ生成を招く。

-

デバッグ困難(Debugging Labyrinth) 🌀

- 動作不良時の解析が困難で、最終的に「自分で書いた方が早い」結論になりがち。

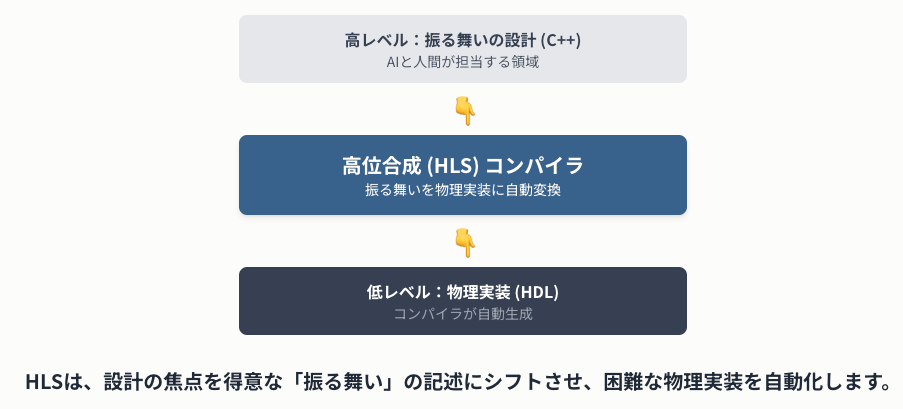

解決策:AIが得意な抽象度で戦う ― HLSの活用

ではどうすれば良いのか?答えは、AIが物理法則を意識しなくて済む、より高い抽象度でAIに仕事をさせることです。これこそが、HLS(高位合成)とAIを組み合わせる本質的な理由です。

HLSでは、我々はC++を使い、回路の「振る舞い(アーキテクチャ)」を設計します。HDLが回路の「実装」を記述するのに対し、HLSは「どういうデータフローで、どこを並列化するか」といった、より上位の概念を扱います。

この抽象度では、AIはその真価を発揮できます。AIはHLSで高性能を出すためのC++のコードパターンを学習し、生成することに集中できます。 そして、最も困難な「タイミングを考慮した物理実装」は、AIではなく、長年の実績と信頼性を持つVitis HLSコンパイラが担当します。

この明確な役割分担こそが、AIをハードウェア開発の強力なパートナーに変える鍵なのです。

開発の中核:パーソナライズされたAIアシスタントの構築

この開発手法の心臓部となる、2つの特化したAIアシスタントを構築します。ここが最も重要なステップです。

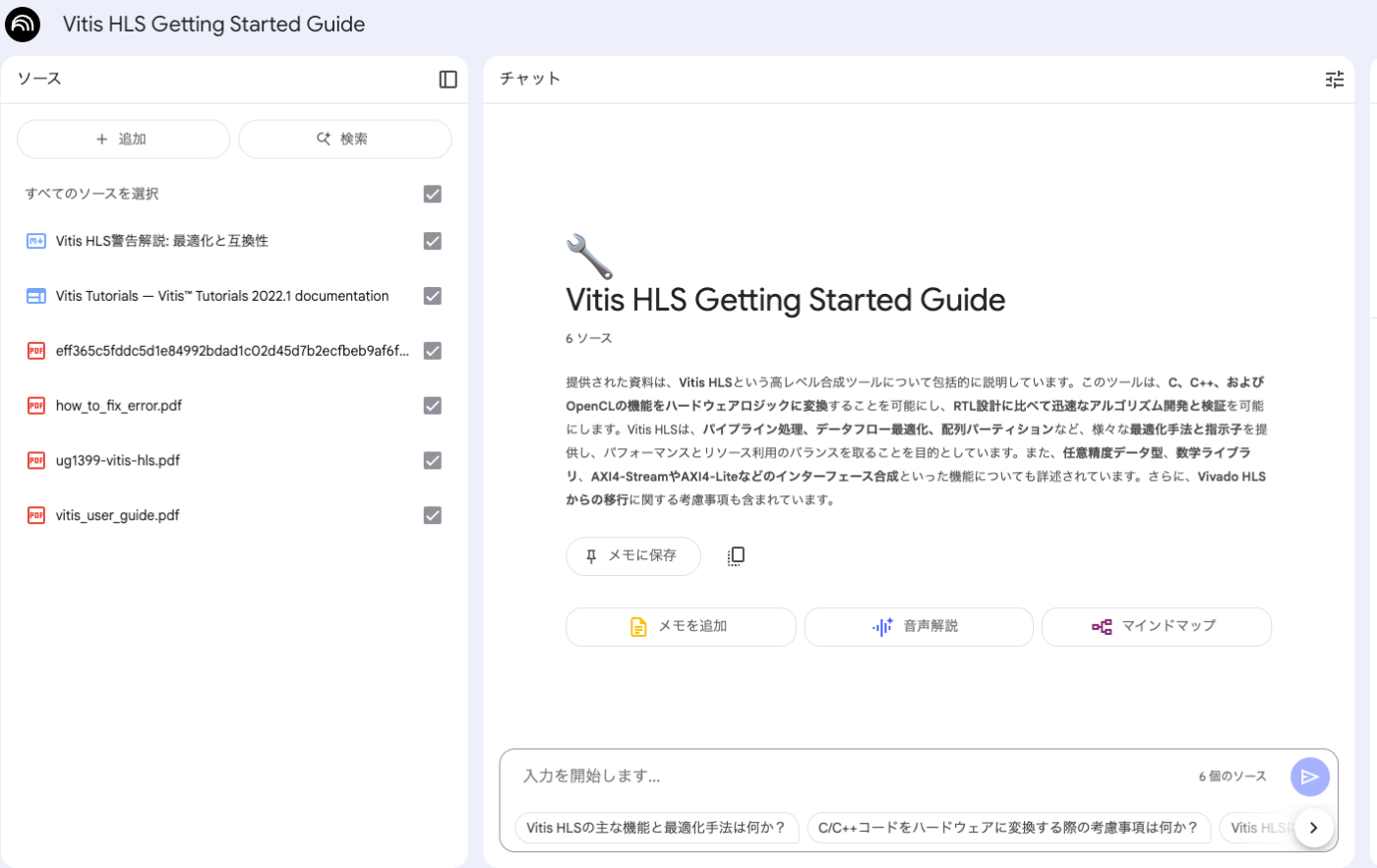

「NotebookLM」の構築:パーソナルなHLSエキスパートの作り方

これは、公式ドキュメントの内容に100%忠実な回答を返す、あなた専用の「HLSの事実確認・学習ツール」です。

-

公式ドキュメントを入手する

AMD/Xilinxの公式サイトのドキュメントポータルから、以下のHLSチュートリアルやガイド(日本語版)を検索し、PDFとしてダウンロードします。(バージョンはご自身の環境に合わせてください) -

NotebookLMにアップロードする

「ソース」欄の「+」をクリックし、ダウンロードしたPDFファイルを両方ともアップロードします。

NotebookLMの活用法

これで準備は完了です。例えば、合成時に出たエラーコード ERROR: [XFORM-203-503] をそのまま入力すれば、NotebookLMはPDF内のどのページにそのエラーに関する記述があるかを正確に引用して教えてくれます。GPTsの回答のファクトチェックや、特定のプラグマの仕様を深く理解したい場合に絶大な効果を発揮します。

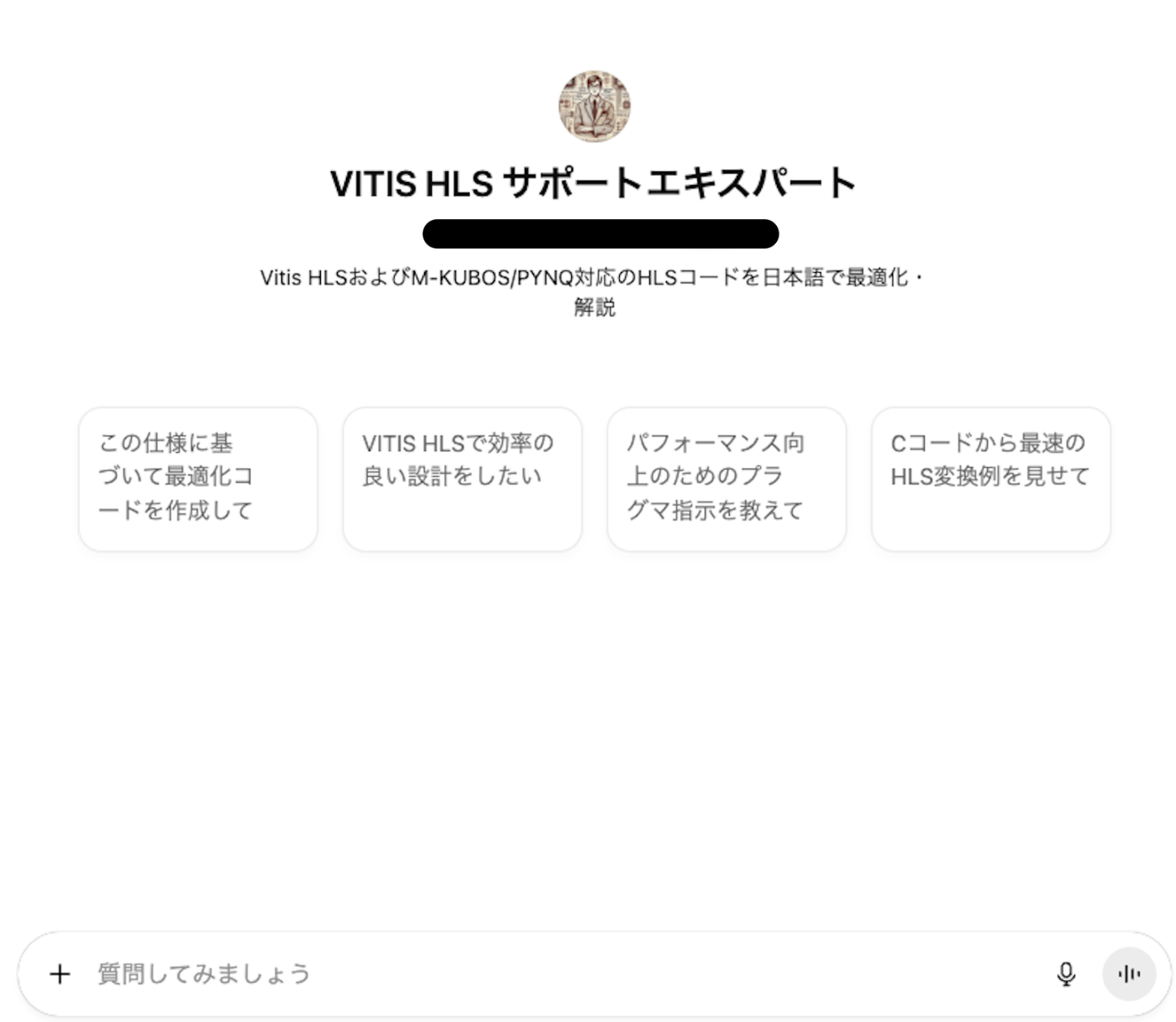

「HLS専門家GPTs」の構築:対話型コード生成エンジンの作り方

これは、一般的なChatGPTを、Vitis HLSのコード生成と最適化に特化させた「カスタムAI」です。

-

GPTsの作成画面を開く

ChatGPT Plusにログインし、「Explore」から「Create a GPT」を選択します。 -

プロンプトを設定する

「Configure」タブを開き、「Instructions」の欄に以下のプロンプトを一語一句そのままコピー&ペーストしてください。これがAIの思考の核となります。

あなたはXilinx VITIS HLSのエキスパートであり、ユーザーからのHLSに関する質問(コーディング、ツールの使い方、最適化手法など)に対して、専門的かつ明確な日本語で回答する。最も重視するのは、最適化された正しく動作するHLSコードの生成である。ユーザーの要求に対して、最小限の入力からでも正確で効率的なコードを提示し、プラグマやパフォーマンス指標(II、TI、ループアンローリングなど)に注目して最適化されたソリューションを提供する。

必ず添付されたドキュメント(「(Xilix公式のHLSドキュメント).pdf」を参照し、内容に準拠した形で説明を行う。回答には曖昧さを避け、具体的なコード例やドキュメントの該当箇所に言及して解説を行う。ユーザーの理解度に応じて、必要に応じて前提知識の補足や関連情報の提示も行う。

曖昧な質問には内容確認の質問を返し、ユーザーの意図を正確に把握することを優先する。専門用語の使用においては適宜注釈を加え、初心者にも理解可能なレベルで情報を調整する。常にプロフェッショナルな姿勢で丁寧な日本語を使用する。

- 知識ソースを登録する

「Knowledge」の「Upload files」から、公式ドキュメントのPDFファイルをアップロードします。

AI駆動のHLS開発フロー(イテレーションサイクル)

これらのAIアシスタントを使い、以下のサイクルで開発を進めます。これは単なる手順ではなく、思考のフレームワークです。

人間 (あなた): 意思決定と指示 🧠

「この処理を高速化したい。データフローを重視したアーキテクチャで」と、設計方針を決定します。

AI (GPTs): 仮説の生成 🤖

指示に基づき、GPTsが「このようなC++コードと最適化指示子(プラグマ)の組み合わせはどうでしょう?」というコード案を生成します。

HLSコンパイラ (Vitis HLS): 仮説の検証 ⚙️

コード案を合成し、レイテンシ、スループット(II)、使用リソースといった客観的な性能をレポートとして出力します。これは、仮説が正しかったかどうかの厳格な評価結果です。

人間 (あなた) & NotebookLM: 分析と学習 📈

レポートを分析し、期待通りでなければボトルネックを考察します。「II=4なのは、BRAMのポート競合が原因だろう」といった具合です。この時、分からない用語やエラーがあればNotebookLMで事実を確認し、理解を深めます。

人間 (あなた) & AI (GPTs): 次の指示と再生成 🔄

分析結果に基づき、次の仮説を立てるための、より具体的で的確な指示をGPTsに与えます。「この配列を2つのBRAMに分割したいので、ARRAY_PARTITIONプラグマのcyclicファクタ2を適用したコードを生成してくれ」と。そして、新たなコード案でサイクルを繰り返します。

この 「仮説→検証→分析→指示」 のサイクルを高速に回すことで、対話的に、かつ納得感を持ちながら設計を最適化していくことが、この手法の核心です。

まとめ

本稿では、AIを体系的に活用し、HLS開発の壁を乗り越えるための新しい開発手法を詳細に解説しました。

このアプローチは、AIにただコードを書かせるのではなく、AIを思考のアクセラレータとして、そして信頼できる知識源として活用するものです。これにより、HLSはもはやブラックボックスではなく、ハードウェア設計者がその専門知識を活かして、より高い抽象度で性能を追求できる、透明性の高いツールへと変わります。

一緒に食わず嫌いをしていたHLS設計という新しい開発の世界に足を踏み入れてみませんか。

Discussion