Magnetic Tunnel Junction-based Computational Random-Access Memory

Figures

Fig. 1 : Illustrations of CRAM concept, features, and potential applications.

a, b Compared to a conventional computer architecture (a), which suffers from the memory-logic transfer bottleneck, CRAM (b) offers significant power and performance improvements. Its unique architecture allows for computation in memory, as well as, random access, reconfigurability, and parallel operation capability. c The CRAM could excel in data-intensive, memory-centric, or power-sensitive applications, such as neural networks, image processing, or edge computing (c).

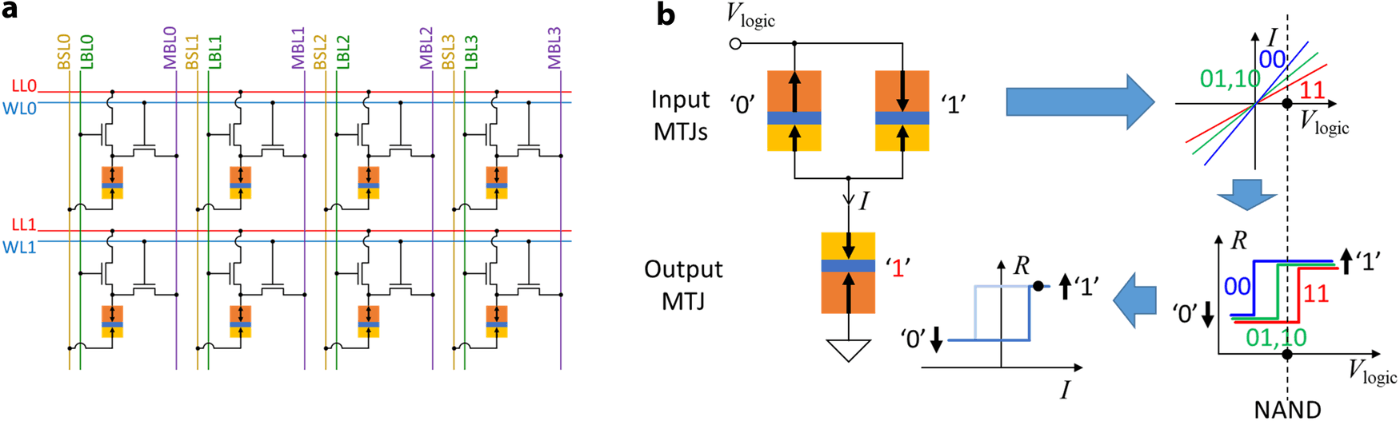

Fig. 2 : Illustrations of the CRAM cell architecture and the working principle of CRAM logic operation.

a CRAM adopts the so-called 2 transistor 1 MTJ (2T1M) cell architecture. On top of the 1T1M cell architecture of STT-MRAM, an additional transistor, as well as the added logic line (LL) and logic bit line (LBL), allow the CRAM to perform logic operations. During a CRAM logic operation, the transistors and lines are manipulated to form an equivalent circuit, as shown in b. Although CRAM can be built based on various emerging memory devices, we use MTJs and MTJ-based CRAM as an example for illustration purposes. b The working principle of CRAM logic operation, the VCL, utilizes the thresholding effect that occurs when switching an MTJ and the TMR effect of the MTJ. With an appropriate

Fig. 3 : CRAM experimental setup.

The setup consists of custom-built hardware and a suite of control software. It demonstrates a fully functioning 1 × 7 CRAM array. The hardware consists of a main board hosting all necessary electronics except for the MTJ devices; a connection board on which passive switches, connectors, and magnetic bias field mechanisms are hosted; and multiple cartridge boards that each have an MTJ array mounted and multiple MTJ devices that are wire bonded. The gray-scale scanning electron microscopy image shows the MTJ array used. The color optical photographs show the cartridge board and the entire hardware setup. The software is responsible for real-time measurements of the MTJs; configuration and execution of CRAM operations: memory write, memory read, and logic; and data collection. It is run on a PC, which communicates wirelessly with the main board.

Fig. 4 : Experimental results for CRAM logic operation.

a Output logic average,

Fig. 5 : CRAM 1-bit full adder demonstration results.

a, b Illustrations of the ‘MAJ + NOT’ and ‘all-NAND’ 1-bit full adder designs. Green and orange letter symbols indicate input and output data for the full adder, respectively. From left to right, numbered by ‘logic step,’ each drawing shows the intended input (green rectangle) and output (orange rectangle) cells involved in the logic operation. The text in purple under each drawing indicates the intended function of the logic operation (MAJ3, NAND, or MAJ5). c–f Experimental (c, d) and simulation (e, f) results of the output accuracy of 1-bit full adder operations by CRAM with the MAJ + NOT (c, e) and all-NAND (d, f) designs. The CRAM adder’s outputs, S and Cout, are assessed against the expected values, i.e., their truth table, for all input states of A, B, and C. The accuracy of each result for each input state is shown by the numerical value in black font, as well as, represented by the color of the box with red (or blue) indicating wrong (or correct), or accuracy of 0% (100%). The accuracy is calculated based on the statistical average of outputs obtained by repeating the full adder execution n times, for n = 10,000. The experimental results for the MAJ + NOT (c) and all-NAND (d) designs are obtained by repeatedly executing the operation for all input states and observing the output states. The simulation results for the MAJ + NOT (e) and all-NAND (f) designs are obtained with probabilistic modeling, using Monte Carlo methods. The accuracy of individual logic operations is set to what was observed experimentally.

Fig. 6 : CRAM accuracy projections.

a NAND gate minimum error rate vs. MTJ TMR ratio with various

要約

この論文は、磁気トンネル接合 (MTJ) を用いた計算用ランダムアクセスメモリー (CRAM) の実験的な実証と評価に関するものである。主な内容は以下の通り:

-

CRAM はメモリーセル自体で論理演算を行うことで従来のコンピューティングパラダイムの限界を克服する新しいアプローチである

-

研究者らは 1×7 CRAM アレイのハードウェアを実験的に実証し、基本的なメモリー操作と論理演算を評価した

-

2 入力 NAND ゲートで 99.4% の精度を達成したが入力数が増えると精度は低下した

-

1 ビット全加算器を CRAM で実装し、最大 78.5% の精度を達成した

-

実験結果に基づいて確率モデルを開発し、CRAM の計算精度を特徴付けた

-

このモデルを使用してスカラー加算、乗算、行列乗算などの基本演算の精度を評価した

-

MTJ 技術の改善により CRAM の精度はさらに向上する可能性がある

-

CRAM は、機械学習などのデータ集約型アプリケーションに大きな影響を与える可能性がある。

この研究は CRAM の実現可能性を実験的に示し、その特性を詳細に分析することでメモリー内計算の新しいパラダイムの基礎を築いている

磁気トンネル接合

磁気トンネル接合 (Magnetic Tunnel Junction, MTJ) はスピントロニクスの分野で重要な役割を果たす素子。以下に MTJ の主な特徴と動作原理を説明する:

-

構造:

- MTJ は 2 つの強磁性層の間に薄い絶縁層(通常は酸化マグネシウム MgO)を挟んだ構造を持つ

- 一方の強磁性層は固定層、もう一方は自由層と呼ばれる

-

動作原理:

- トンネル磁気抵抗 (TMR) 効果を利用している

- 2 つの強磁性層の磁化の相対的な向きによって素子の電気抵抗が変化する

-

状態:

- 平行状態:両方の強磁性層の磁化が同じ方向を向いている状態。低抵抗状態

- 反平行状態:強磁性層の磁化が逆向きの状態。高抵抗状態

-

情報の記録と読み出し:

- 記録:スピン転移トルク (STT) 効果を利用して自由層の磁化方向を変更する

- 読み出し:素子の抵抗を測定することで記録された情報を読み取る

-

応用:

- 不揮発性メモリ (STT-MRAM)

- スピントロニクスデバイス

- 磁気センサー

-

利点:

- 不揮発性:電源を切っても情報が保持される

- 高速動作:ナノ秒オーダーでの読み書きが可能

- 低消費電力:特に待機時の消費電力が低い

-

課題:

- さらなる微細化と高密度化

- 信頼性と耐久性向上

- TMR 比向上

MTJ は従来の半導体技術とは異なるアプローチで情報を処理・記憶することができるため次世代のコンピューティングデバイスとして期待されている。この論文で紹介されている CRAM は MTJ のこれらの特性を活かしてメモリー内で直接計算を行うという革新的なアプローチを実現している

電源を切っても情報が保持される仕組み

MTJ(磁気トンネル接合)が電源を切っても情報を保持できる理由は、その動作原理と物理的特性に基づいている。以下にその主な要因を説明する:

-

磁化の安定性 :

- MTJ の情報は強磁性層の磁化方向によって保持される

- 強磁性体の磁化は外部からのエネルギー入力がない限り安定した状態を維持する

- この安定性は材料の磁気異方性によって提供される

-

非揮発性メカニズム :

- 電子のスピンに基づいて情報を記録するため電荷の蓄積に依存しない

- 従来の半導体メモリー(DRAM 等)とは異なりリフレッシュ動作が不要である

-

エネルギー障壁 :

- 磁化の反転には一定のエネルギー障壁を超える必要がある

- この障壁が熱擾乱に対する耐性を提供し室温でも情報を保持できる

-

磁気モーメントの量子力学的性質 :

- 磁気モーメントは量子力学的に離散的な状態をとる

- これにより中間状態ではなく明確な「0」または「1」の状態を維持する

-

材料選択と設計 :

- 適切な材料選択と層構造の設計により長期間の情報保持が可能になる

- 例えば高い磁気異方性を持つ材料を使用することで熱安定性を向上させる

-

電気的分離 :

- MTJ の構造上、強磁性層は電気的に分離されている

- これにより電源がオフの状態でも電荷の漏れによる情報の損失がない

-

磁気ヒステリシス :

- 強磁性体は磁気ヒステリシスを示し一度設定された磁化状態を保持する傾向がある

- これにより外部磁場や電流がない状態でも情報が保持される

これらの特性により MTJ は電源を切っても情報を保持することができ、不揮発性メモリーとして機能する。この特性は省電力化や即時起動が可能なデバイスの開発に大きく貢献している。CRAM のような新しいコンピューティングパラダイムではこの不揮発性を活用してメモリーと演算を効率的に統合している

自由層のヒステリシス特性

磁気トンネル接合 (MTJ) では主に自由層のヒステリシス特性を利用して情報を記録し保持する。以下に詳細を説明する

-

固定層と自由層の役割

- 固定層:磁化方向が固定されており参照点として機能する

- 自由層:磁化方向を変更可能で情報の記録に使用する

-

自由層のヒステリシス利用

- 情報の記録:自由層の磁化方向を変更することで行う

- 情報の保持:自由層の磁気ヒステリシスにより設定された磁化状態が維持される

-

固定層の役割

- 固定層は磁化方向が変化しないため自由層の状態を読み取る際の基準点として機能する

- TMR 効果を利用した読み出しの際、固定層と自由層の相対的な磁化方向が重要になる

-

書き込み操作

- スピン転移トルク (STT)などの手法を用いて自由層の磁化方向を反転させる

- この際、固定層の磁化方向は変化しない

-

読み出し操作

- MTJ の抵抗を測定することで自由層の磁化状態(固定層との相対的な向き)を判断する

-

エネルギー障壁

- 自由層の磁化反転には一定のエネルギー障壁を超える必要がある

- この障壁が情報の安定性と不揮発性を保証する

-

設計上の考慮

- 自由層のヒステリシス特性は安定性と書き込み容易性のバランスを考慮して設計される

- 固定層は強い磁気異方性や反強磁性層との交換結合などにより高い安定性を持つように設計される

-

熱安定性

- 自由層の熱安定性は情報保持時間に直接影響する

- 適切な材料選択と層構造により長期間の情報保持が可能になる

したがって MTJ においては主に自由層のヒステリシス特性を利用して情報を記録し保持するが、固定層も読み出し操作や全体的なデバイス性能に重要な役割を果たしている。CRAM のような応用では、この自由層の制御可能な磁化状態を利用してメモリー機能と論理演算機能を統合している

論理演算を行う仕組み

CRAM における論理演算では MTJ の特性と電気的な制御を巧みに組み合わせている。以下にその仕組みを段階的に説明する

-

基本原理:電圧制御論理 (Voltage-Controlled Logic, VCL)

- MTJ の抵抗状態(高抵抗 / 低抵抗)を論理状態 (1/0) に対応させる

- 複数の MTJ を電気的に接続しそれらの組み合わせた抵抗値を利用して論理演算を行う

-

CRAM セルの構造

- 各セルは 1 つの MTJ と 2 つのトランジスタで構成されている(2T1M 構造)

- これによりメモリー機能と論理演算機能の両方が可能になる

-

論理演算の設定

- 特定の MTJ を入力として選択し別の MTJ を出力として設定する

- 選択された MTJ をロジックライン (LL) を介して一時的に接続する

-

電圧印加

- 入力 MTJ に電圧パルスを印加し出力 MTJ は接地する

- 印加する電圧の大きさ(

V_{logic}

-

電流制御

- 入力 MTJ の抵抗状態に応じて出力 MTJ に流れる電流が変化する

- この電流の大きさが出力 MTJ の状態を決定する

-

スイッチング閾値の利用

- MTJ のスイッチング(磁化反転)には閾値電流がある

- 入力の組み合わせによってこの閾値を超えるかどうかが決まる

-

論理演算の実現

- 例えば NAND 演算の場合 入力が "11" の時のみ出力 MTJ がスイッチしないように電圧を調整する

- 他の入力組み合わせでは出力 MTJ がスイッチし結果として NAND 論理が実現される

-

並列処理

- CRAM アレイ内の複数の行で同時に同じ演算を行うことができ大規模な並列処理が可能である

-

再構成可能性

- 印加電圧(

V_{logic}

- 印加電圧(

-

確率的な性質

- MTJ のスイッチングは本質的に確率的なプロセスである

- これにより CRAM の論理演算は確率的な性質を持ち複数回の演算の平均値として結果を得る

この仕組みにより CRAM はメモリー内で直接論理演算を行うことができデータの移動を最小限に抑えつつ効率的な計算を実現している。この特性は特にデータ集約型のアプリケーションや機械学習タスクにおいて大きな利点となる可能性がある

確率的計算

確率的計算 (Probabilistic computation) は CRAM における重要な特性であり、その動作原理と応用に深く関わっている。以下に確率的計算の詳細を説明する

-

基本概念

- CRAM の論理演算は決定論的ではなく確率的な性質を持つ

- 結果は単一の演算ではなく複数回の演算の統計的な平均として得られる

-

MTJ のスイッチング特性

- MTJ の磁化反転(スイッチング)は本質的に確率的なプロセスである

- 印加される電流や電圧および持続時間によってスイッチング確率が変化する

-

確率的論理ゲート

- CRAM の論理ゲート(NAND AND OR など)は確率的に動作する

- 入力の組み合わせに対して出力が確率的に決定される

-

エラー率と精度

- 各論理演算には一定のエラー率が存在する

- エラー率は MTJ の特性 動作条件 および回路設計に依存する

-

統計的平均化

- 同じ演算を複数回実行し結果の統計的平均を取ることで精度を向上させる

- 演算回数を増やすことで決定論的な結果に近づける

-

エラー耐性

- 確率的な性質により一部のエラーに対して自然な耐性を持つ

- これは特に機械学習や近似計算などの応用で有利に働く

-

スケーラビリティー

- 大規模な CRAM アレイでは多数の並列演算が可能

- 統計的な効果により全体的な精度が向上する可能性がある

-

エネルギー効率とのトレードオフ

- 高精度を求めると演算回数が増加しエネルギー消費が増える

- 応用に応じて精度とエネルギー効率のバランスを取る必要がある

-

応用分野

- 機械学習:確率的な性質が学習アルゴリズムと親和性が高い

- 近似計算:厳密な結果が不要な場合に効率的に利用できる

- 確率的アルゴリズム:CRAM の特性を活かした新しいアルゴリズムの開発が可能

-

課題と展望

- エラー率の低減:MTJ 技術の向上や回路設計の最適化が必要

- モデリングと解析:確率的動作の正確なモデル化と性能予測が重要

- アーキテクチャー設計:確率的計算の特性を活かしたシステム設計の研究が進行中

確率的計算は CRAM の本質的な特性であり従来の決定論的な計算とは異なるアプローチを提供する。これにより新しい計算パラダイムや応用の可能性が開かれると同時に独自の課題も生まれている

電圧制御論理

電圧制御論理 (Voltage-Controlled Logic, VCL) は CRAM における論理演算の基本原理である。以下に VCL の詳細を説明する

-

基本概念

- MTJ の抵抗状態を利用して論理状態を表現する

- 電圧の制御によって論理演算を実現する

-

MTJ の状態表現

- 低抵抗状態(並行磁化)を論理 "0" とする

- 高抵抗状態(反並行磁化)を論理 "1" とする

-

回路構成

- 複数の MTJ を電気的に接続する

- 入力 MTJ と出力 MTJ を指定する

- ロジックライン (LL) を介して MTJ 間を一時的に接続する

-

電圧印加

- 入力 MTJ に一定の電圧 (

V_{logic} - 出力 MTJ は接地する

- 入力 MTJ に一定の電圧 (

-

電流制御

- 入力 MTJ の抵抗状態に応じて電流が変化する

- この電流が出力 MTJ に流れスイッチングの可能性を決定する

-

スイッチング閾値

- MTJ のスイッチングには閾値電流が存在する

- 入力の組み合わせによってこの閾値を超えるか決まる

-

論理関数の実現

-

V_{logic} - 例:NAND 演算では入力 "11" の時のみ出力がスイッチしないよう設定する

-

-

確率的性質

- スイッチングは確率的プロセスであるため論理演算も確率的になる

- 複数回の演算の平均として結果を得る

-

並列処理

- CRAM アレイ内で複数の VCL 演算を同時に実行できる

-

再構成可能性

-

V_{logic}

-

-

エネルギー効率

- データ移動を最小限に抑えメモリー内で直接計算を行う

- 従来の CMOS 論理に比べ低消費電力の可能性がある

-

課題

- エラー率の制御:MTJ 特性のばらつきや熱ノイズの影響を考慮する必要がある

- 動作速度:MTJ のスイッチング速度が全体の性能に影響する

-

応用展望

- データ集約型アプリケーション:メモリー内計算の利点を活かせる

- 機械学習:並列処理と確率的性質が適している

VCL は CRAM の核心技術であり従来の論理回路とは異なるアプローチで計算を実現する。この技術は新しいコンピューティングパラダイムの基礎となり特定の応用分野で大きな潜在力を持っている

Discussion