Tang Nano 9k で開発を始めるためのメモ

やること

Tang Nano 9k で何がしか開発をするときの、最初の手順のメモです。

開発環境の準備

Gowin EDA をダウンロードしてインストールする。バージョン 1.9.9 以上を使用すること。

プロジェクトの作成

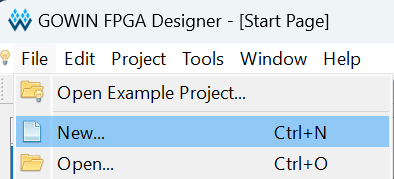

メニューから New を選ぶ。

FPGA Design Project を選ぶ。

適当なプロジェクト名を入れる。

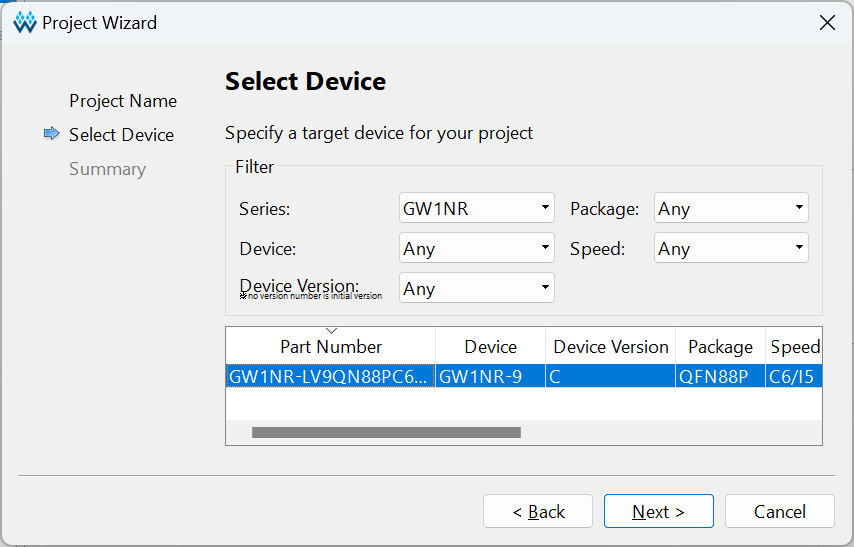

Series で GW1NR を選び、Part Number で GW1NR-LVQN88PC6/15 を選ぶ。

これでOKを押すとプロジェクトが作成される。

SyatemVerilog を使う場合の設定

特にこだわりがないなら System Verilog にしておくといろいろ幸せ(多分)。

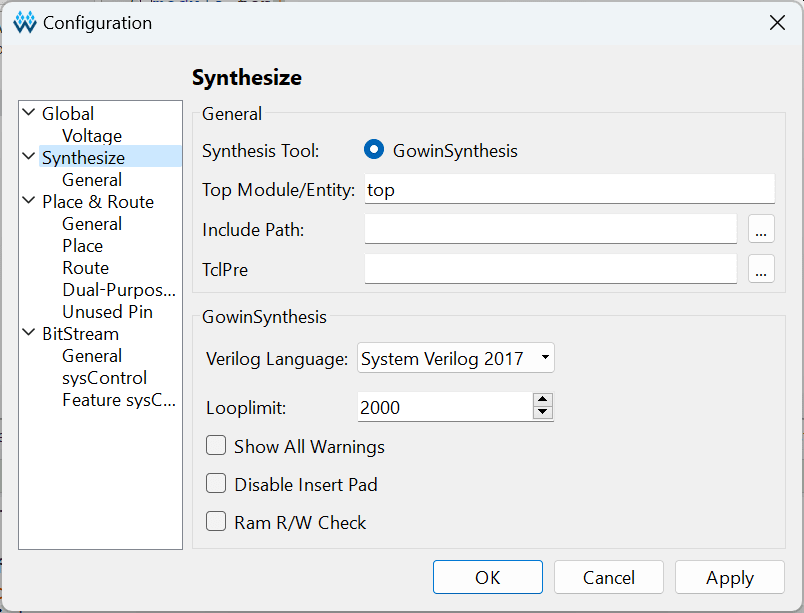

Project のメニューから Configuration を選ぶ。

Synthesize の項目を選んで、Verilog Language から System verilog 2017 を選ぶ。これで OK を押す。

Verilog ファイルの作成

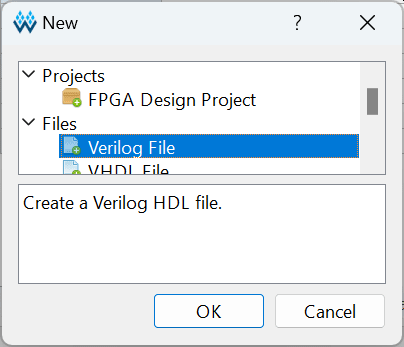

New を選んで、Verilog File を選ぶ。

ファイル名を入れる。SystemVerilog を使うときは、拡張子を .sv にする。OK を押すとファイルが生成される。もし左側にファイルを選ぶUIが表示されないときは、画面左下の Device のタブを押すと表示される。

コードを書く。

`default_nettype none

module top (

input wire IN_A,

input wire IN_B,

output wire OUT_A,

output wire OUT_B

);

assign OUT_A = IN_A & IN_B;

assign OUT_B = IN_A | IN_B;

endmodule

`default_nettype wire

書いたらセーブしておく。

Configuration で Top Module にモジュール名を設定しておく。ここでは top にしている。

設定したら OK しておく。

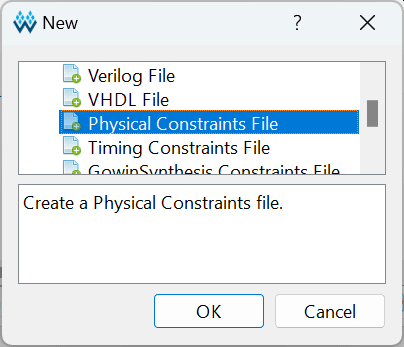

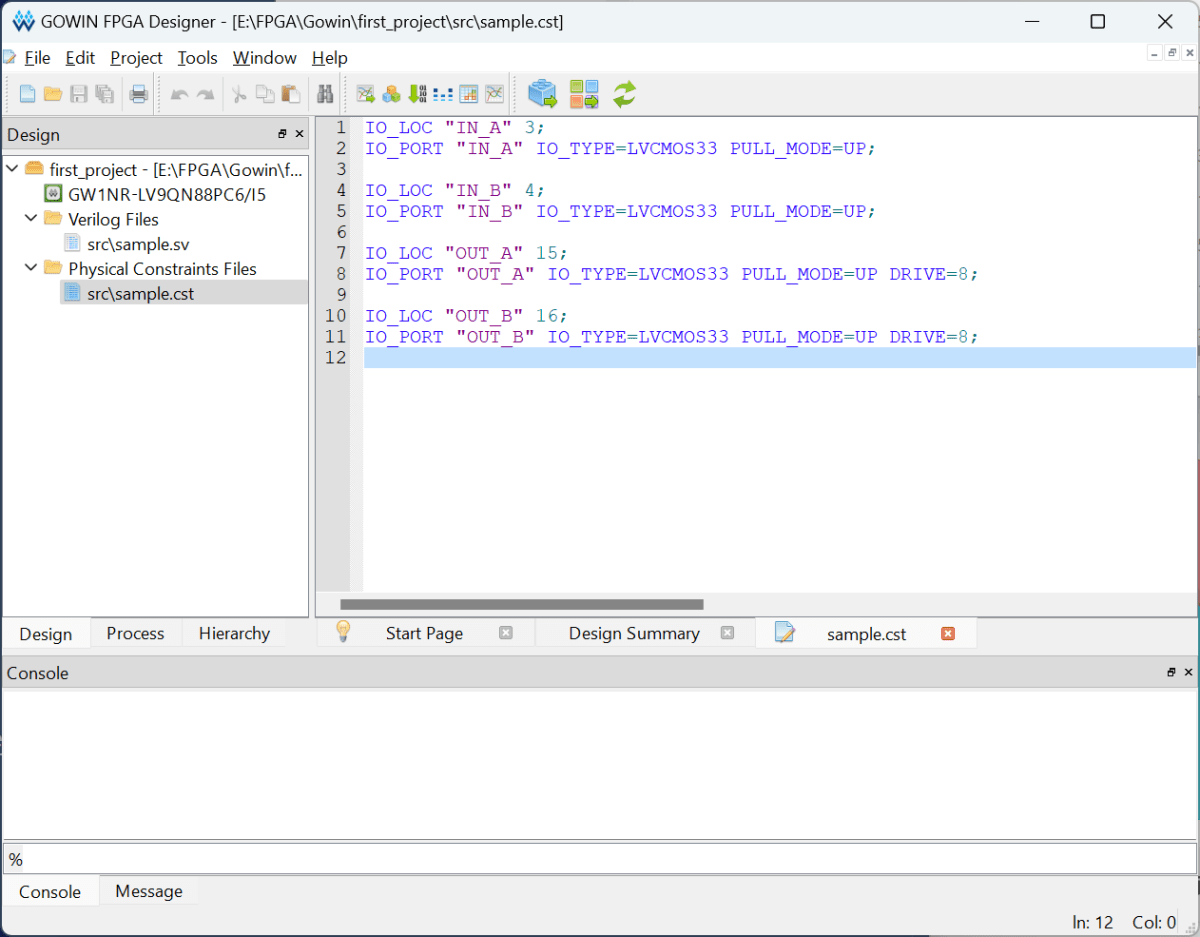

物理制約ファイルの作成

New を選んで、Physical Constraints File を選ぶ。

適当なファイル名を入れる。

物理制約を記述する。

2つのスイッチにINを割り当てて、OUTはLEDを割り当てている。

IO_LOC "IN_A" 3;

IO_PORT "IN_A" IO_TYPE=LVCMOS33 PULL_MODE=UP;

IO_LOC "IN_B" 4;

IO_PORT "IN_B" IO_TYPE=LVCMOS33 PULL_MODE=UP;

IO_LOC "OUT_A" 15;

IO_PORT "OUT_A" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "OUT_B" 16;

IO_PORT "OUT_B" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

ドキュメントは下記。

Synthesize, Place, Route

Run Place & Route を押す。メニューから選んでもいい。

これで Route までは終わる。エラーがあったらエラーが Console に表示されるので直す。

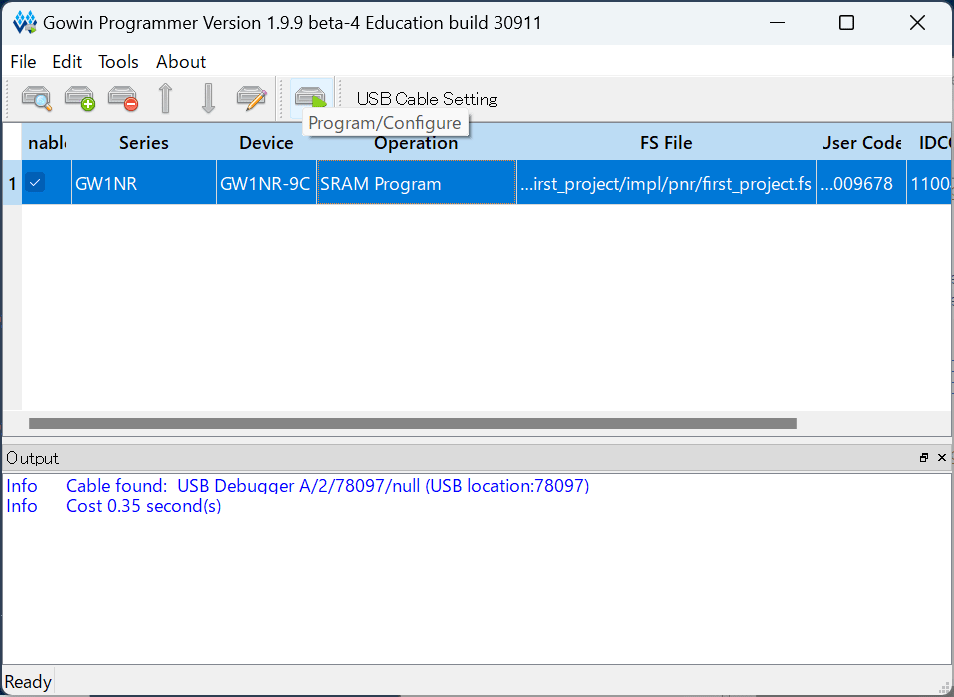

Program

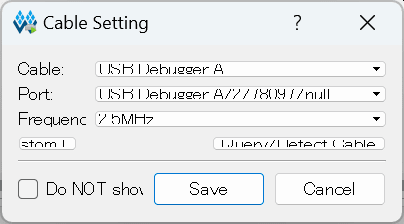

Tang Nano 9k を USB ケーブルで接続しておく。Tools から Programmer を選ぶ。

下のような画面が出たら、Save を押しておけばOK(多分)。

GW1NR を選んでから Program/Configure のボタンを押す。

Tang Nano 9k との接続が正常にできていて、Route までエラーなく処理できていれば、この状態で書き込めるはず。

動作確認

Tang Nano 9k 上にある二つのスイッチの、片方だけ押すと LED が1つだけ点灯し、両方押すと LED が2つ点灯するという動作になるはず。

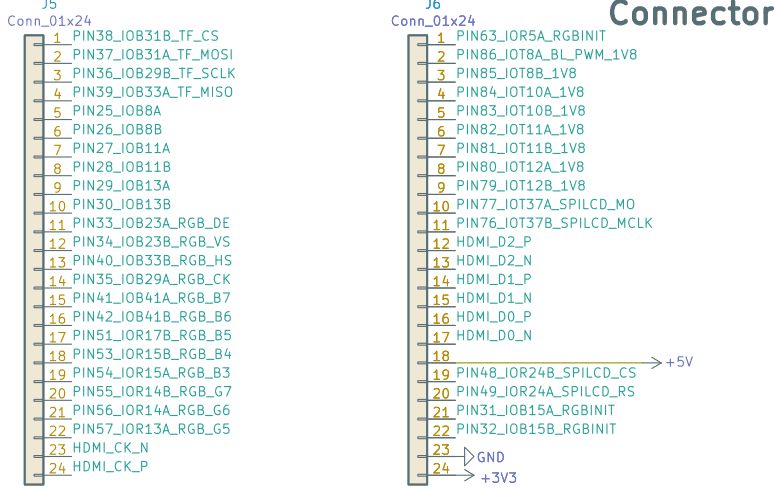

ピン配置

下記に回路図がある。

以下はコネクタに出ているピンだけ抜粋したもの。ちなみに CLK は 52 番ピン。

タイミング制約

SDC ファイルを直接書いてもいいけど、Tools から Timing Constraints Editor を使ったほうが幸せ(多分)。詳しくは下記。

Discussion