Microchip FPGAのセキュリティについて

Flash-basedのFPGAは高セキュリティだという話は以前から聞いていた。これは外付けROMを持たないからそこのビットストリーム窃取がありえないという意味くらいだと思ってたし、マーケティングの側面が強いワードだろうと思っていた。

しかし聞くところによると、どうもそれ以上のものがあるらしいので調べてみた。

フラッシュFPGAの特徴

- 高速起動(コンフィグレーション読み込みが発生しないので)

- 低消費電力

- スタティック消費電力が限りなく小さい

- 突入電流の削減

- ダイナミック電力がどうかという疑問はある。トランジスタの数でみれば確かにフラッシュのほうが有利だが、SRAMベースはVersalとか7nmで、フラッシュは高々28nm

- ソフトエラーに強い

- そもそもフラッシュを書き換えるには高電圧が必要なのでSRAMベースよりソフトエラー(コンフィグレーションの書き換えのみ?)に強い

- いわゆる1Tセルではなく2Tで1ビット保持するっぽい。

製品ファミリ

まず大枠としてFPGA/SoC FPGA/Ra-Tolerant(RT) FPGAの3つがある。FPGAはふつうのやつ。SoC FPGAはいわゆるZynq的な、ハードCPUが入ってるやつで、RT FPGAは航空宇宙用というか、ソフトエラー耐性を高めたやつだろう。

FPGAs

4つのファミリがある

-

PolarFire

- ミッドレンジ

- 一部の製品にはCrypto co-processorが付属しており、DPA耐性とTRNGが入っている。CRIのIPを使っているようである。

- System ControllerにはPUFとSecure sNVMがある。

- Tamper Detectors & Countermeasuresという部分もあり、かなり耐タンパーに配慮しているように見える。

-

IGLOO2

- PCIeやGbit etherを含んだ汎用用途?

- アーキテクチャ図ではFlash-basedの部分とStandard cellの部分があるのだが、SRAMベースを含むという意味か?一方で図的には全部Flash-basedにも見える。よくわからん。

- System ControllerのところにAES/SHAに加え楕円やSRAM-PUFが入ってる。

-

IGLOO

- 超省電力、省スペース

- スリープモードへの高速移行

-

ProASIC

- Lowest-Power, Low-Density FPGAs in Smallest Packages

- Cortex-M1 ソフトコア

SoC FPGAs

- PolarFire

- PolarFire FPGAに5コアRISC-Vハードコアを追加したもの

- PolarFire FPGAに5コアRISC-Vハードコアを追加したもの

- SmartFusion2

- IGLOO2あたりにCortex-M3を入れたものかな?

- IGLOO2あたりにCortex-M3を入れたものかな?

- SmartFusion

- IGLOOあたりにCortex-M3を入れたもの?

Rad-Tolerant FPGAs

5ファミリあるがあまり重要でないので触れない。

例えばRT PolarFireはPolarFireに耐放射線性を持たせたものであるが、ブロック図的にはふつうのPolarFireと変わらなかった。

どうやって耐放射線性をあげてるのか気になるが、プロセスを変えてるのか、パッケージを変えてるのか、誤り訂正を入れてるのかとか?

ツール側で3重冗長系をサポートしてるっぽい

セキュリティ

PolarFireファミリが最も高いセキュリティ機能を持っているっぽい。以下の資料が詳しい。

またYoutubeにある動画 なども参考になる。

全体像

System Controller

Root of Trustであり、鍵管理、ビットストリーム認証/復号、システムコール発行などを担当。暗号コプロとしてAthena TeraFire F5200ASRを搭載。AES/SHA/TRNG(NRGB)/ECCなどが乗っており、特にAESはCRIのDPA対策版IP?(違うかも)。フラッシュベースなので、ビットストリーム認証/復号って必要なのかな?と思うが、リモートアップデートの時とかに使うっぽい?SoCの場合はファームウェアアップデートの場合もあるだろうし、セキュアブートのためにECCも使うのだろう。SBIC_MIN_VERSION?カウンタを持っており再生攻撃もできないようにしている。

またシステムコントローラ(だけ?)はアクティブメッシュで保護されておりプロービングできない。バススクランブル・誤り訂正・スクラビング(全アドレスに自動的にアクセスして、誤り訂正する)も入ってるらしい。

引用元:Microchip社の動画(https://www.youtube.com/watch?v=LT-YYXjeVZM)

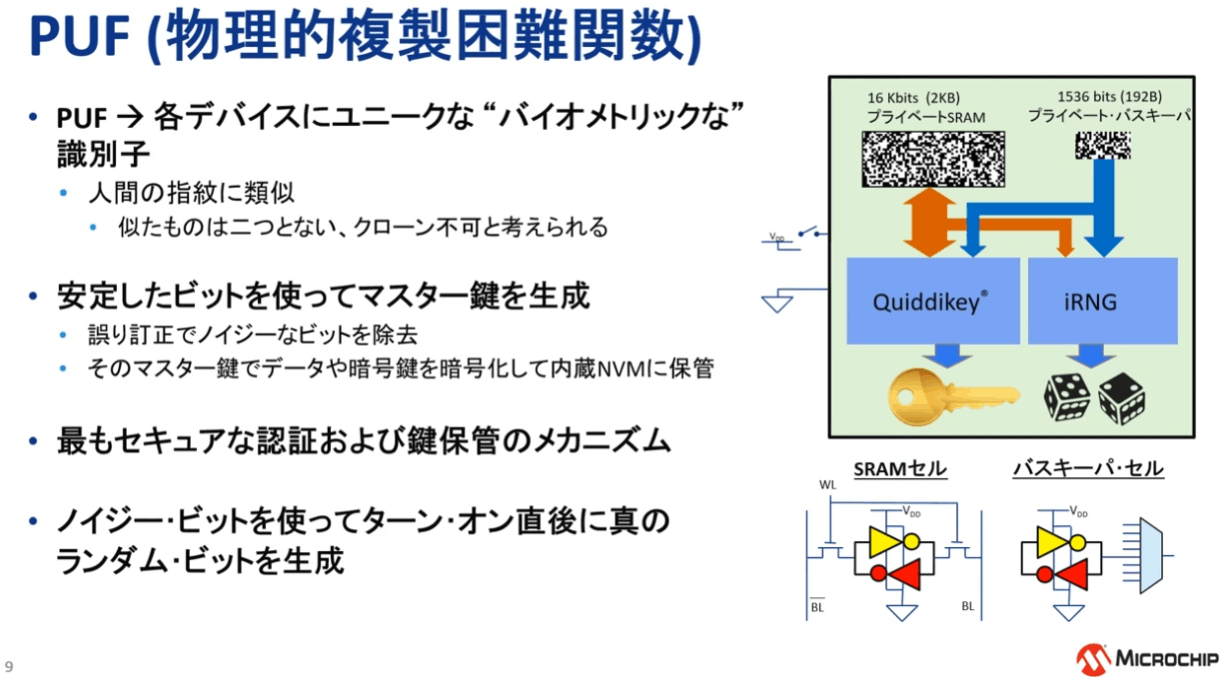

SRAM-PUF

Intrinsic-ID社のPUF IPでデバイス固有鍵と乱数生成を行っている(いわゆるTRNGはここのことか?)。

Quiddikey-Flex IPによる誤り訂正で、不安定なPUF出力から安定なユニークマスター鍵を作る。マスター鍵で鍵やデータを暗号化して内臓NVMに保存するため、内臓NVMが攻撃されても、PUFが見えなければ意味がない。PUFは短い時間しか通電されないため、安全。

二つのマスター鍵があり、1つはデザイン・セキュリティ・キーのラッピングに使用され、もう1つはセキュア不揮発性メモリ(sNVM)の暗号化と認証機能に使用される。

引用元:Microchip社の動画(https://www.youtube.com/watch?v=TXM0SPYmXjI)

sNVM

256バイト

- Non-authenticated plaintext

- Authenticated plaintext (Available in all PolarFire family “S” version devices)

- Authenticated ciphertext (Available in all PolarFire family “S” version devices)

下のほうがアクセスが遅い。

認証鍵にはユーザーが設定したuser sNVM key (USK)を使う。暗号鍵はPUF secret key(SMK)で暗号化はsynthetic initialization vector (SIV) モード?AES-256。

認証なしの場合はページ当たり252バイト利用可能で、認証付きの場合236バイト。

引用元:Microchip社の動画(https://www.youtube.com/watch?v=TXM0SPYmXjI)

Device-Level Anti-Tamper Features

電圧/クロック/温度センサが、侵襲/非侵襲攻撃をモニタ。検知したらシステムコントローラがファブリックに多数ある専用線の一つを使ってイベントを送信。ユーザーロジックはイベントに対してIOピンの無効化/ロックダウン/ゼロ化などをシステムコントローラーにリクエスト可能。またユーザーからの要求でこれらの機能を使うこともできる。

User Cryptoprocessor and NRBG

型番の最後が"S"になっているデバイスでは、User Cryptoprocessorと呼ばれるデータセキュリティのための専用コア(Athena TeraFire EXP-F5200B)が利用可能。PolarFire SoCの場合はMSSに統合されている。これはファブリックまたはMSSからアクセス可能。

Pass-through License for CRI Patented DPA Protection

Microchip社はCRIとパススルーライセンス契約しているため、ユーザーはライセンス料を払うことなくFPGAにDPA耐性ありの暗号コアを組み込むことができる?

ほか

verifyはon chipで、bitstream read機能はない?

パスコードで暗号鍵書き換え可能

所感

セキュリティの資料がたくさんあってすごいと思う反面、悪用されないか心配になる。

Discussion