Vitisに入門してみる。(1)Lチカ

環境

Vitis 2022.2

Vivado 2022.2

Windows 11

Ubuntu20.04 on WSL2

Arty Z7-20

目標

FPGAによる高速化を考えた時、ロジック側だけでなくやはりソフトとの連携を意識していく必要があるなと考えたので、そろそろVitisを触ってみるかという気持ち。

上記のようなサイトを参考にすると、Vitisは狭義のXilinxツールを指す一方で広義にはVitisによるアクセラレーションフロー全体を指している感がある。

とりあえずVitisを使った高速化のターゲットやワークフローにいろいろあるみたい。

ひとまずターゲットに対しては、

- データセンターアクセラレーション:要はAlveo

- エンベデッドアクセラレーション:要はZynq

の2種類ある模様。

データセンターアクセラレーションはホスト側のおそらくドライバ対応の理由によりLinux環境でしか開発できずめんどいのでエンベデッドでやってみる。

その辺に転がっていたArty Z7-20を使う。

で、アクセラレーションカーネルの書き方に

- RTL (Vivado)

- C/C++ (Vitis HLS)

- OpenCL (Vitis)

の3つのバリエーションがあるみたい。

OpenCLはVitisだけでツールが完結する?なら楽そうだなと思いつつ一番とっつきにくそう。

これらの性能の違いに興味があるので全部やってみようかな。

ひとまず剰余乗算器の実装を目指す。

Vitis Target Platform

のっけから想像と違っていたのだが、Vitisを運用するにはVivadoの使用を避けては通れなさそうなところ。

要はZynqのPS部分を使うためのbitstreamはVivadoで生成しないといけないっぽい。

Xilinx製のZCUボードとかだとビルド済みイメージが提供されてるっぽいのでこのステップはスキップできるらしいが、そうでない場合はこのビルドから。

Zynq Ultrascale+ならVivadoのExampleにそれっぽいのがあるのだが、Zynq-7000にはそういうのない。。。

どうすればVitisの要件を満たすのかわからないが

を参考に何かしら作ってみる。(これはlinuxを使わずPSで動作するのはベアメタルアプリケーションなので、Vitis Platformとは呼ばないのかもしれない)

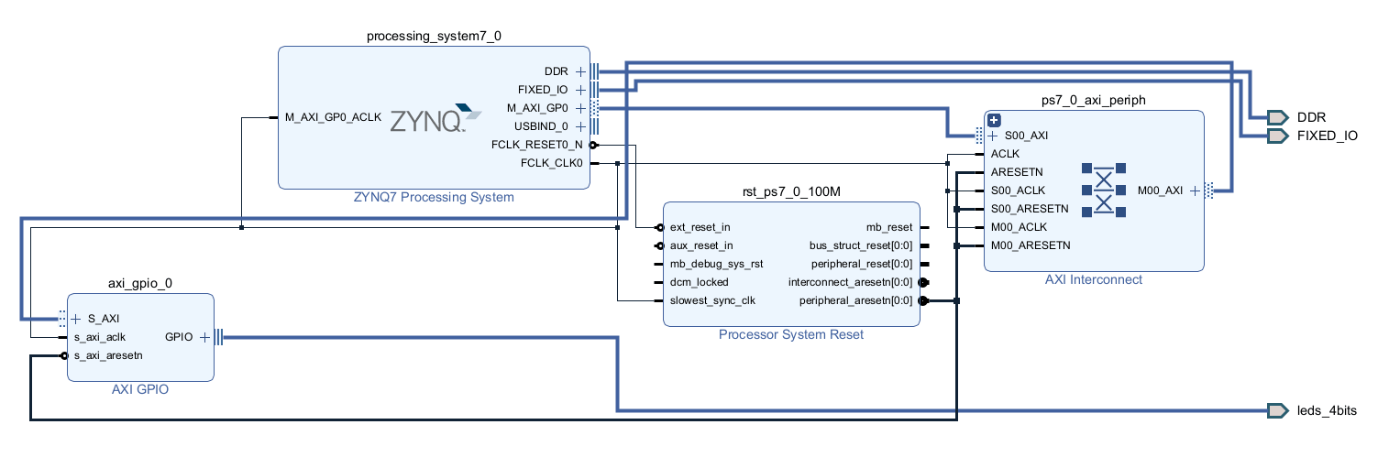

よくあるAXI GPIOのブロックデザイン

ビルド結果。10 ns制約に対してスラック3.611しかないので200 MHzでも動かない?

Export HardwareしてVivadoパートは終了。

Vitis

Exportしたハードウェアは.xsaファイルになっているので、それを読み込んで(アプリケーション)プロジェクトを作成する。

こんな感じで二つプロジェクトが作成される。上がシステムプロジェクトで下がプラットフォームプロジェクト。

ビルドするのは両方のプロジェクトの模様?実行するのはシステムプロジェクトのほう。システムプロジェクトは[led_hardware]ってなってるのでプラットフォームプロジェクトの情報が読み込まれているんだろう。ちなみに実行時に自動ビルドはやってくれない模様。

で実行するとLチカすることができた。

次回へ続く

Discussion